# Hardware-Software Codesign

### **3. Mapping Applications To Architectures**

Lothar Thiele

### System Design

### What is ahead?

#### Section 4: Partitioning

- Some basic methods to assign tasks to computing resources (or communication to networks and busses).

- Section 5: Multiobjective Optimization

- Generic method to optimize H/S systems (and other engineering systems)

#### Section 7: Design Space Exploration

Application of these methods to design space exploration

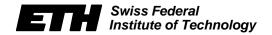

# **System Synthesis - Mapping**

#### Mapping transforms behavior into structure and execution

- allocation: select components

- binding: assign functions to components

- **scheduling**: determine execution order

- … finally, synthesis results into implementation

partitioning

mapping

# **Application Specification**

#### ... using an underlying model of computation

- some examples (see also next slides)

- task graphs: data flow graph, control flow graph

- process networks: Kahn process network, synchronous data-flow

- state machine representations: SpecCharts, StateCharts [not covered in this course]

- for mapping, very often only the process network structure and its (abstract) properties are relevant (abstraction from detailed functionality)

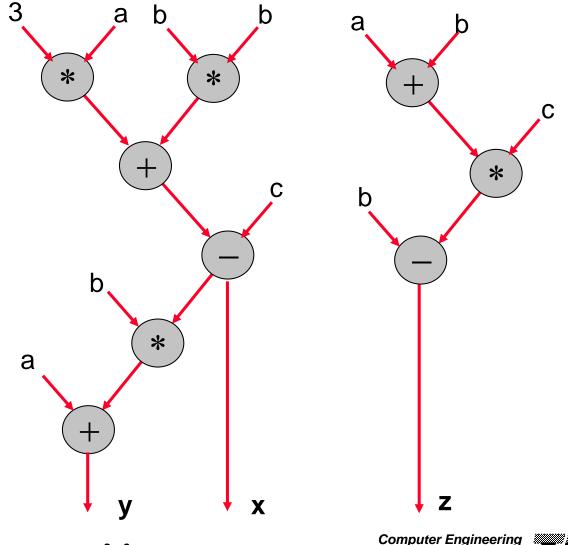

### **Application Specification - Example 1**

data flow graph (DFG)

x = 3\*a + b\*b - c; y = a + b\*x; z = b - c\*(a + b);

and Networks Laboratory

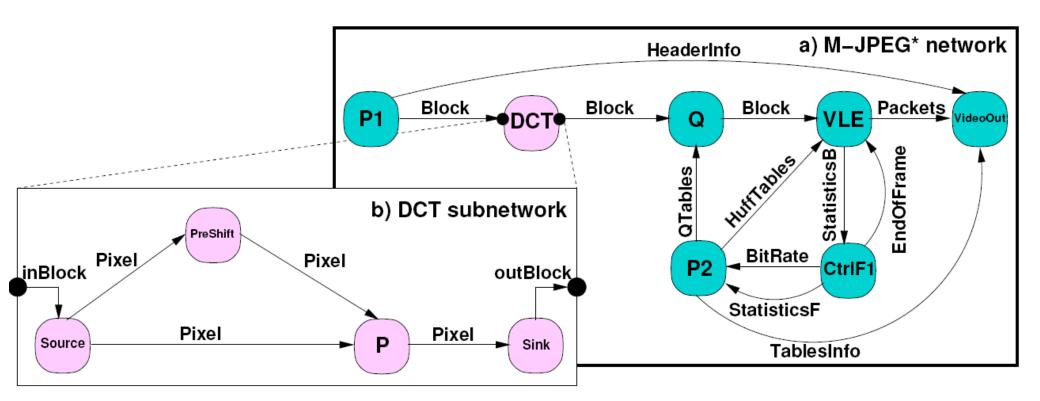

# **Application Specification - Example 2**

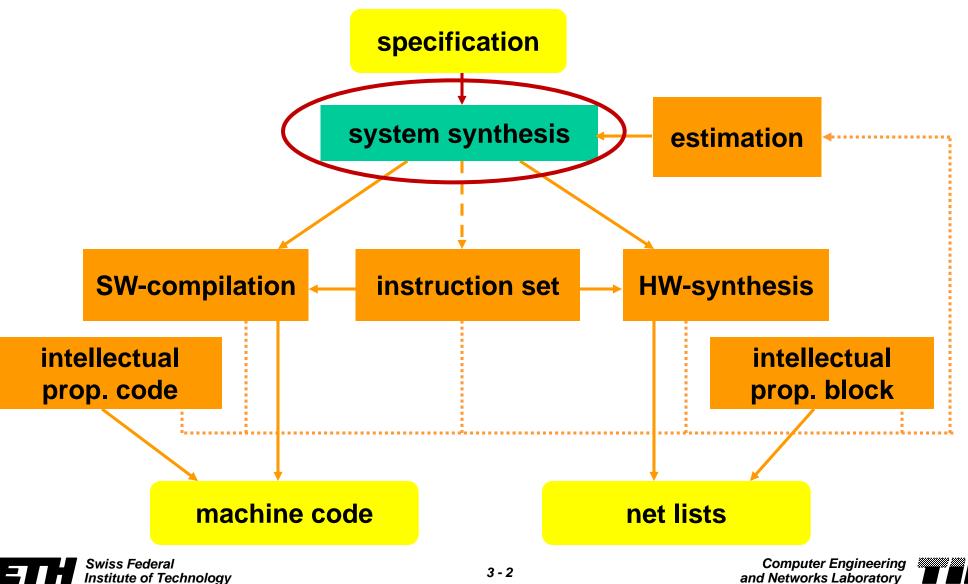

#### Kahn process network

example: hierarchical network of MJPEG application

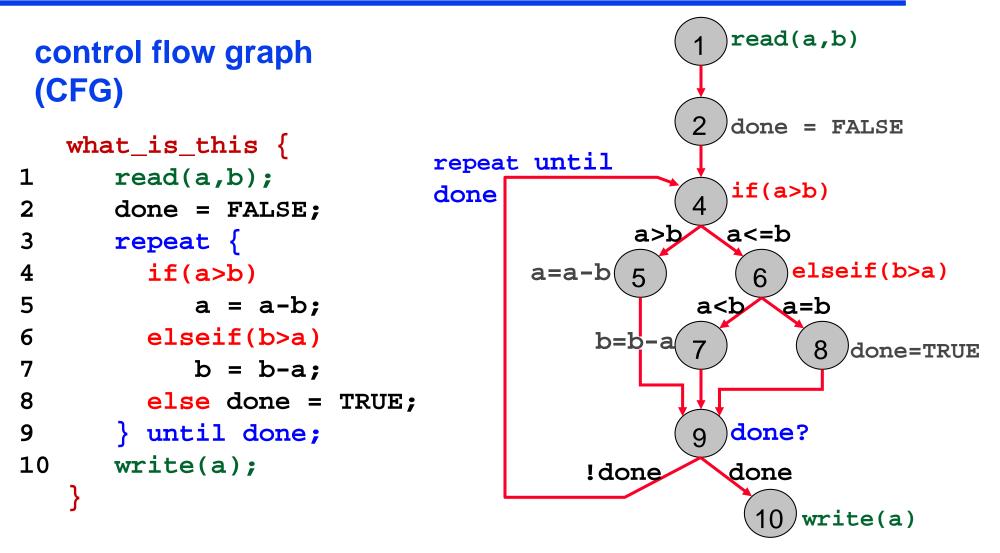

# **Application Specification - Example 3**

Swiss Federal Institute of Technology

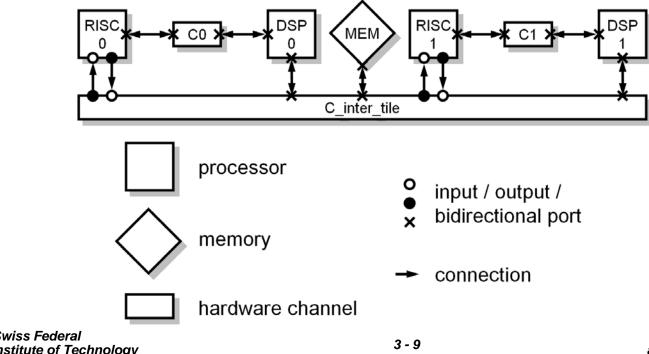

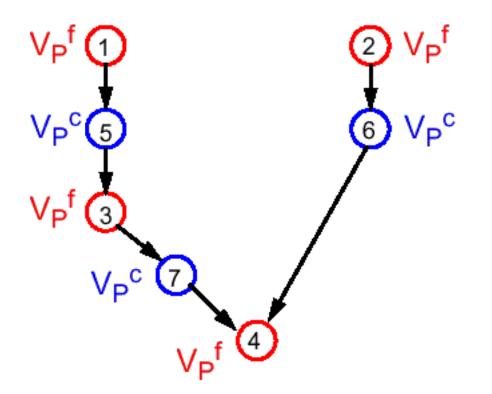

# **Architecture Specification – Example**

- reflects the structure and (key) properties of the underlying platform

- ... and can be done at different abstraction levels

- example: system-level architecture specification

- usually a graph notation is used to describe structure

- annotations to graph elements reflect properties of the underlying platform, e.g., processing frequency

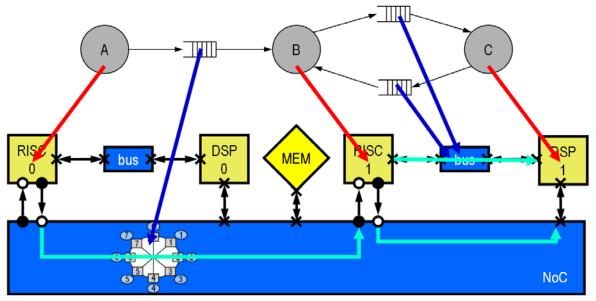

# Mapping Specification - Example

- mapping relates application and architecture specifications

- binds processes to processors

- binds communication between processes to communication paths of the architecture

- specifies resource sharing disciplines and scheduling

Mapping = binding + scheduling

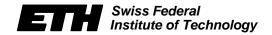

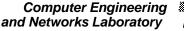

## **Example: DFG Application Model**

basic model: data flow graph and static scheduling

data flow graph  $G_P(V_P, E_P)$

Interpretation:

- V<sub>P</sub> consists of functional nodes V<sub>P</sub><sup>f</sup> (task, procedure) and communication nodes V<sub>P</sub><sup>c</sup>.

- E<sub>P</sub> represent data dependencies

### **Example: Architecture Model**

Architecture graph  $G_A(V_A, E_A)$ :

- V<sub>A</sub> consists of functional resources V<sub>A</sub><sup>f</sup> (RISC, ASIC) and bus resources V<sub>A</sub><sup>c</sup>. These components are potentially allocatable.

- E<sub>A</sub> model directed communication.

# **Example: Mapping**

and Networks Laboratory

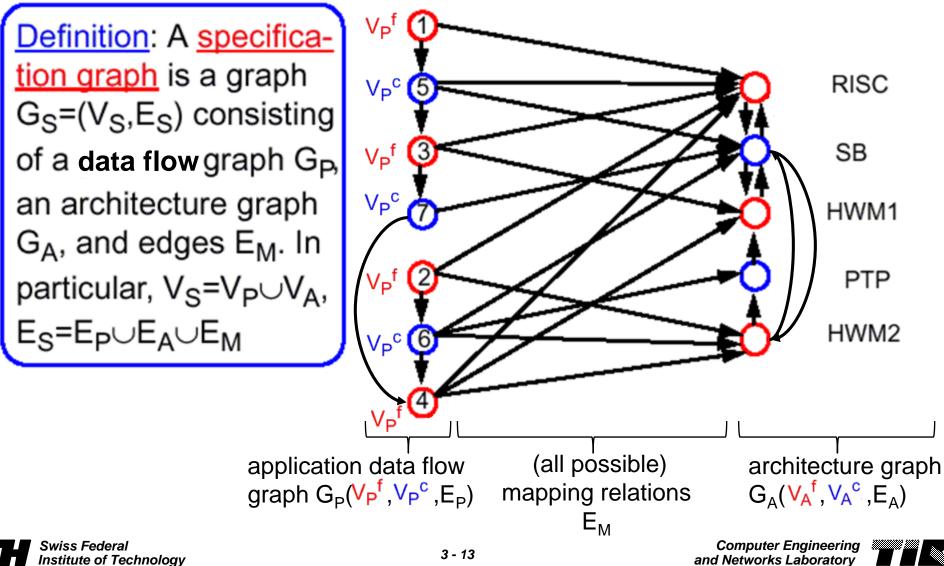

## **Example: Synthesis**

- Synthesis involves

- allocation  $\alpha$  (subset of  $v_A$ )

- **binding**  $\beta$  (subset of  $\mathbf{E}_{\mathbf{M}}$ ), i.e., reflecting the mapping of application nodes in  $\mathbf{V}_{\mathbf{P}}$  (functional and communication) onto architectural nodes in  $\mathbf{V}_{\mathbf{A}}$  (processors and buses)

- scheduling τ, i.e., assigning an order among nodes (e.g., start time)

- ...and ultimately, implementation of (α, β, τ) targeted to actual hardware and/or software modules

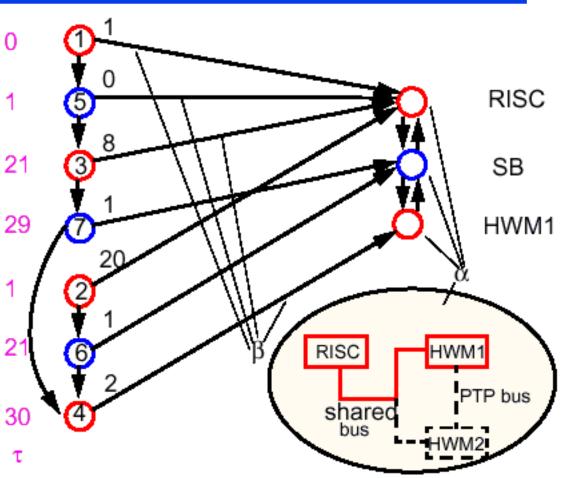

### **Example: ... towards Implementation**

Definition: Given a specification graph  $G_S$ an <u>implementation</u> is a triple ( $\alpha$ , $\beta$ , $\tau$ ), where  $\alpha$ is a feasible allocation,  $\beta$  is a feasible binding, and  $\tau$  is a schedule.

### **Example: ... towards Implementation**

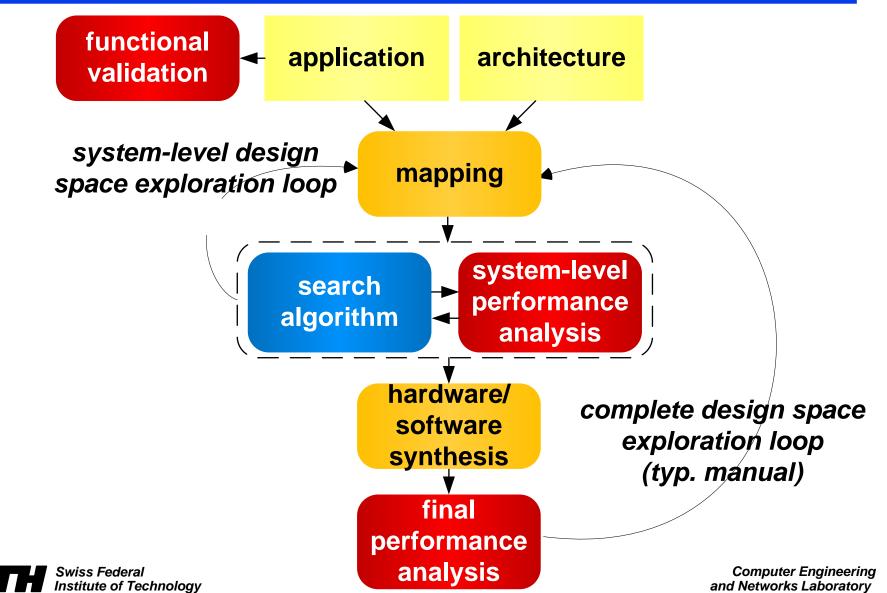

#### Mapping Optimization in the Design Flow

### Mapping Optimization in the Design Flow

- Often based on iterative interaction between optimization and performance analysis

- Based on quantitative parameters obtained through estimation, e.g., end-to-end delay, throughput, power, temperature

### What is ahead?

#### Section 4: Partitioning

- Some basic methods to assign tasks to computing resources (or communication to networks and busses).

- Section 5: Multiobjective Optimization

- Generic method to optimize H/S systems (and other engineering systems)

#### Section 7: Design Space Exploration

Application of these methods to design space exploration