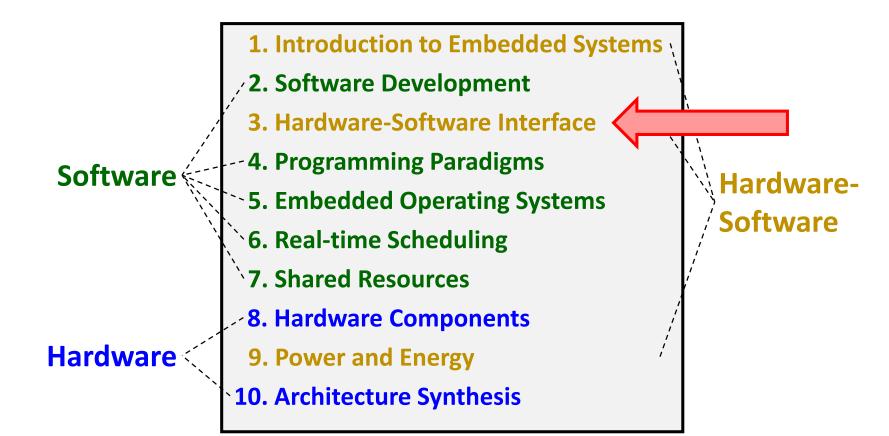

# **Embedded Systems**

### **3. Hardware Software Interface**

© Lothar Thiele

Computer Engineering and Networks Laboratory

### **Do you Remember ?**

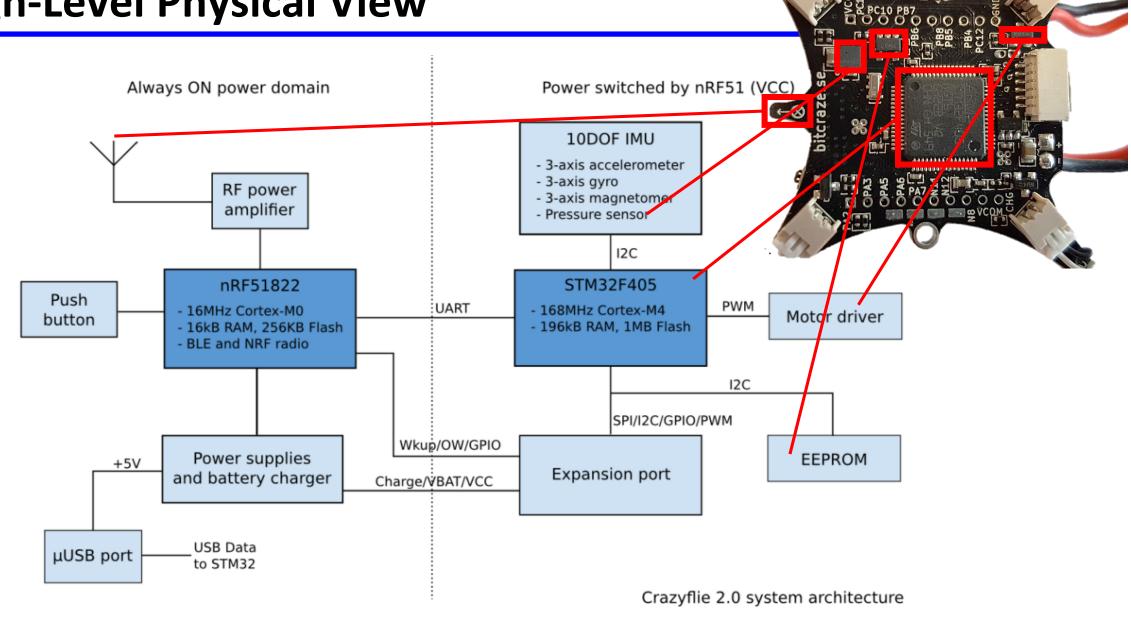

### **High-Level Physical View**

# **High-Level Physical View**

### What you will learn ...

#### Hardware-Software Interfaces in Embedded Systems

- Storage

- SRAM / DRAM / Flash

- Memory Map

- Input and Output

- UART Protocol

- Memory Mapped Device Access

- SPI Protocol

- Interrupts

- Clocks and Timers

- Clocks

- Watchdog Timer

- System Tick

- Timer and PWM

### Storage

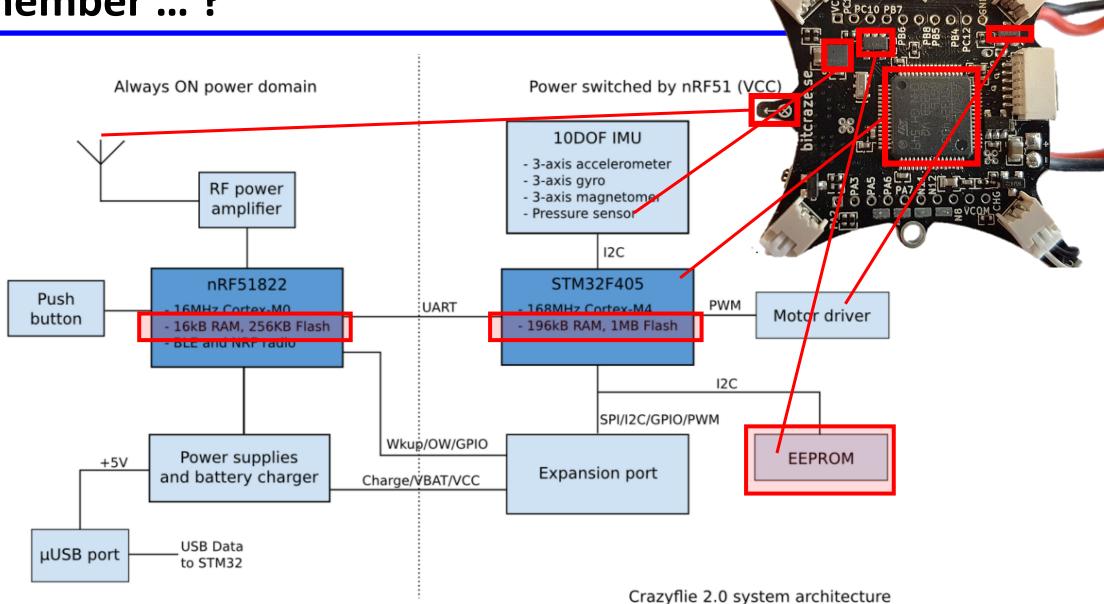

# Remember ... ?

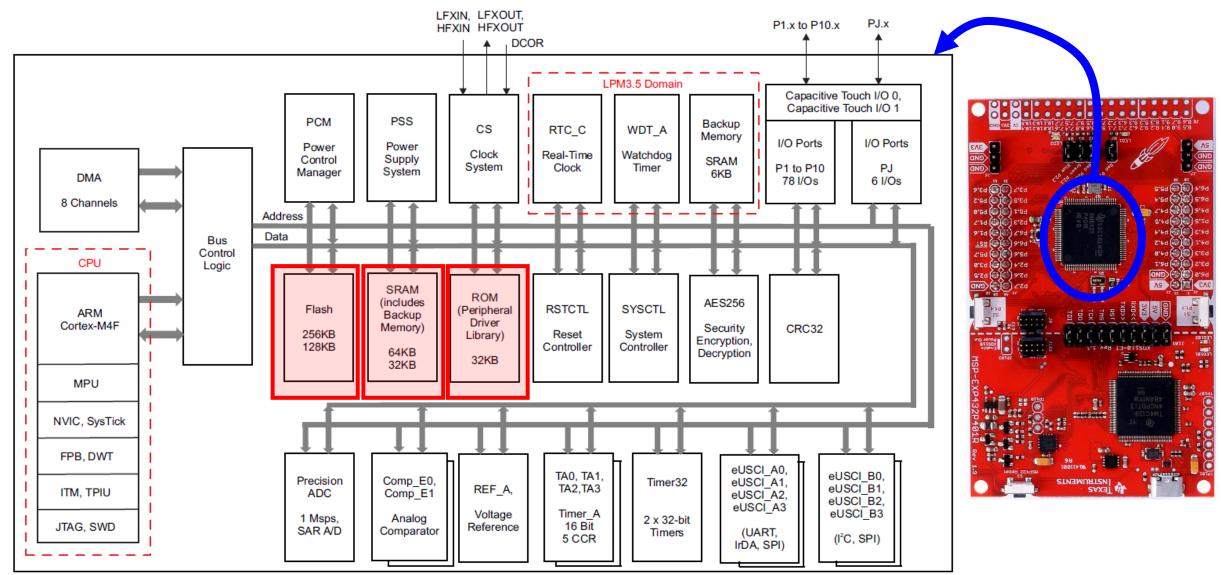

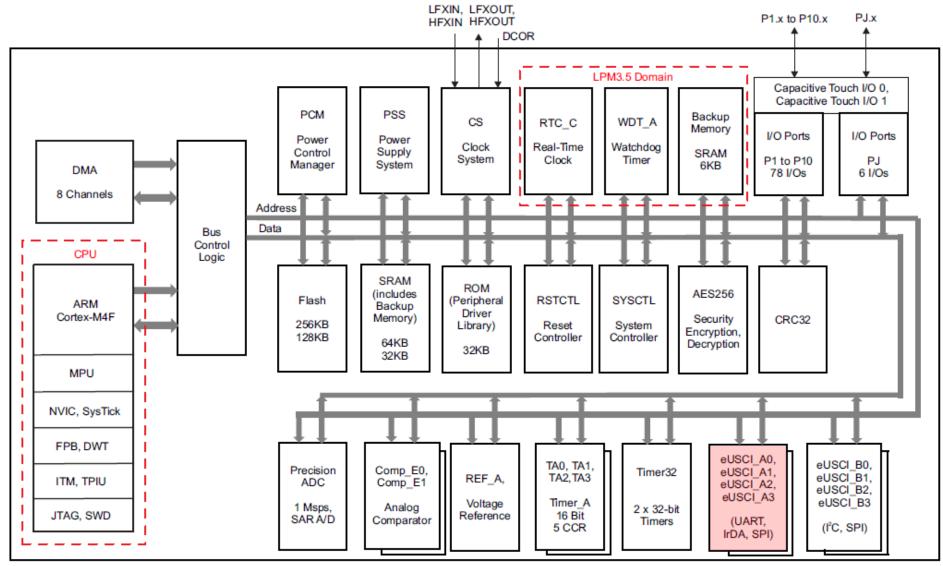

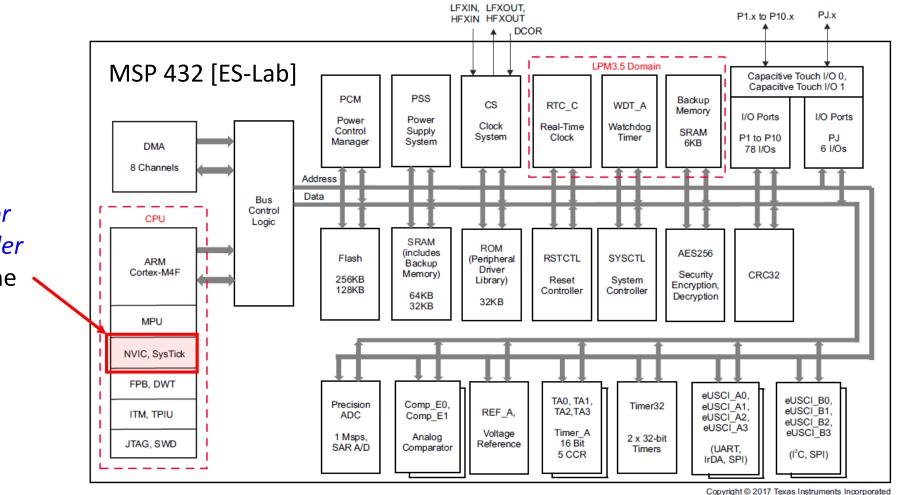

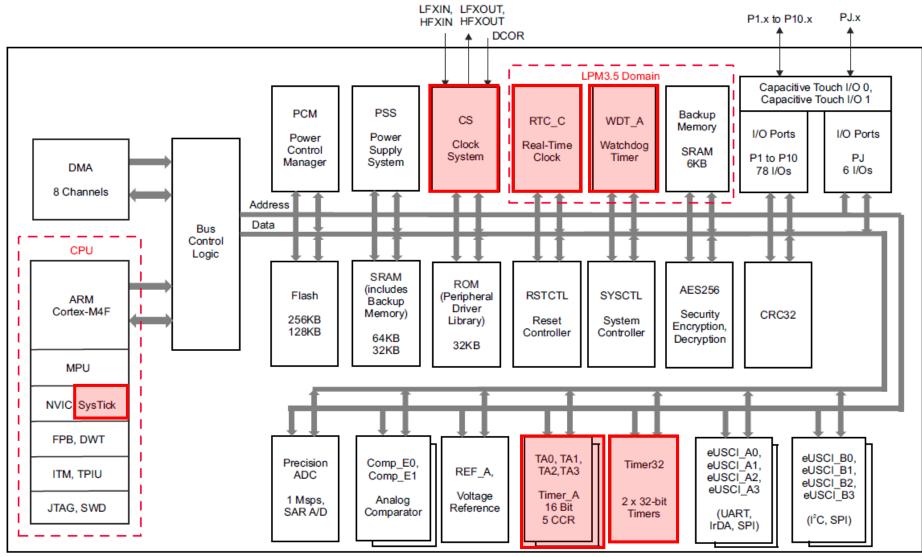

### MSP432P401R (ES-Lab)

# SRAM / DRAM / Flash

1

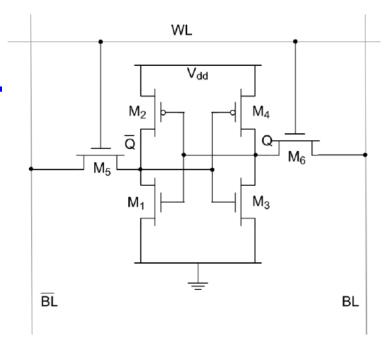

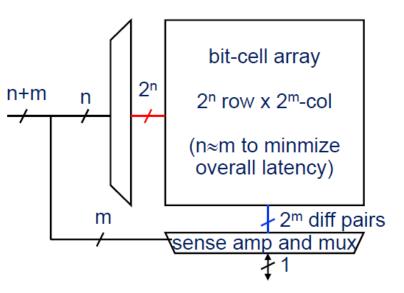

# Static Random Access Memory (SRAM)

- Single bit is stored in a bi-stable circuit

- Static Random Access Memory is used for

- caches

- register file within the processor core

- small but fast memories

- Read:

- 1. Pre-charge all bit-lines to average voltage

- 2. decode address (n+m bits)

- 3. select row of cells using n single-bit word lines (WL)

- 4. selected bit-cells drive all bit-lines BL (2<sup>m</sup> pairs)

- 5. sense difference between bit-line pairs and read out

- Write:

- select row and overwrite bit-lines using strong signals

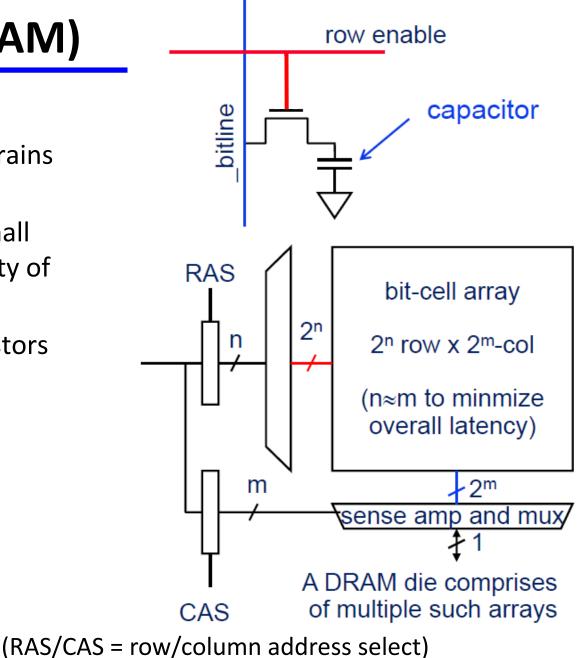

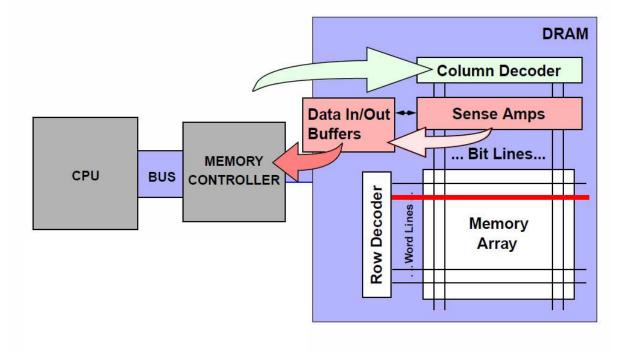

### **Dynamic Random Access (DRAM)**

#### Single bit is stored as a charge in a capacitor

- Bit cell loses charge when read, bit cell drains over time

- Slower access than with SRAM due to small storage capacity in comparison to capacity of bit-line.

- Higher density than SRAM (1 vs. 6 transistors per bit)

#### DRAMs require *periodic refresh* of charge

- Performed by the memory controller

- Refresh interval is tens of ms

- DRAM is unavailable during refresh

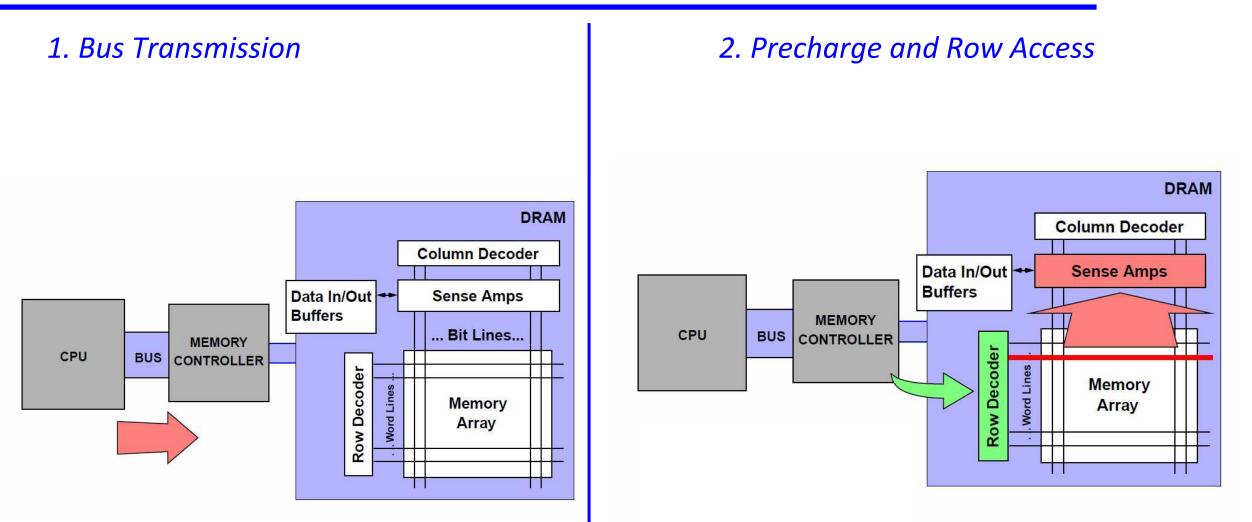

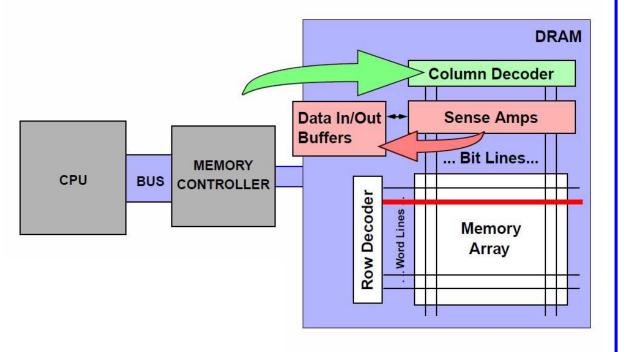

### **DRAM – Typical Access Process**

### **DRAM – Typical Access Process**

3. Column Access

#### 4. Data Transfer and Bus Transmission

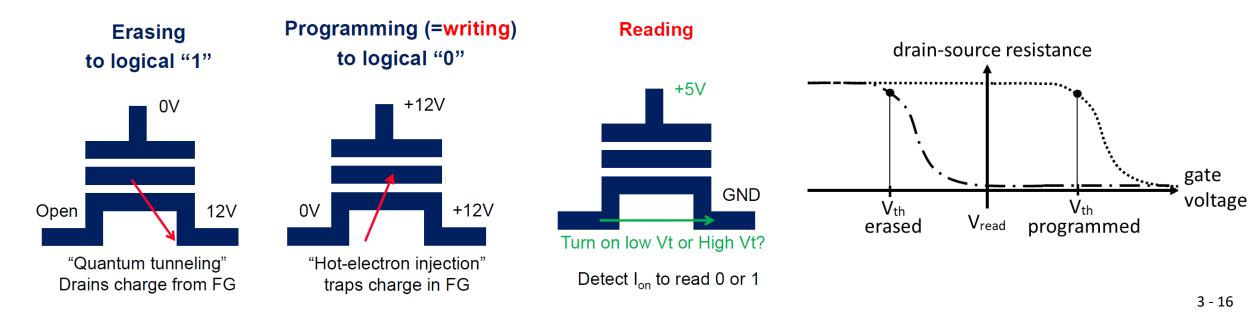

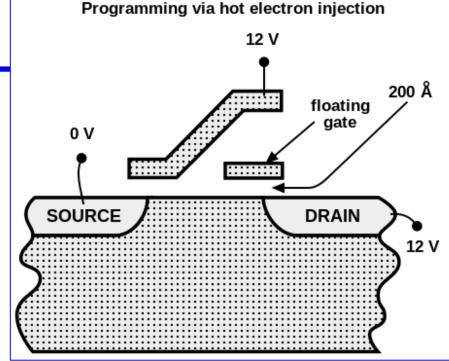

# Flash Memory

Electrically modifiable, non-volatile storage *Principle* of operation:

- Transistor with a second "floating" gate

- Floating gate can trap electrons

- This results in a detectable change in threshold voltage

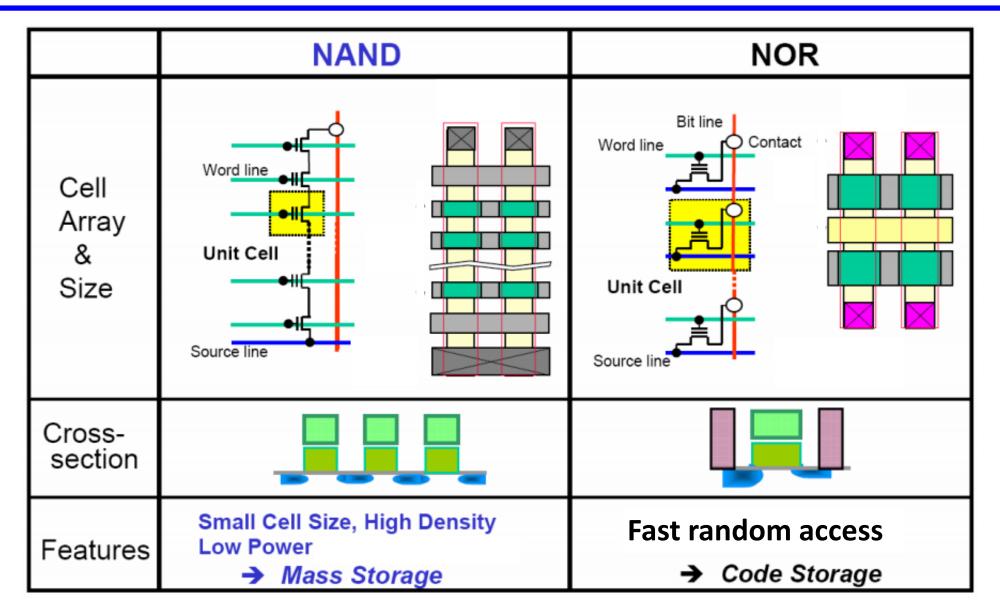

### **NAND and NOR Flash Memory**

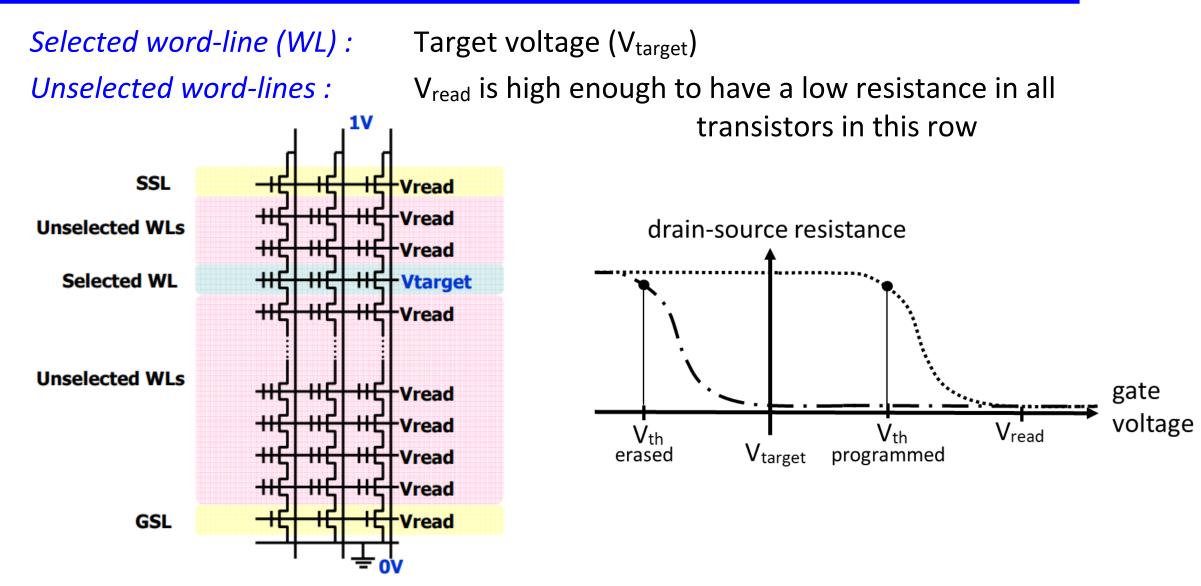

### **Example: Reading out NAND Flash**

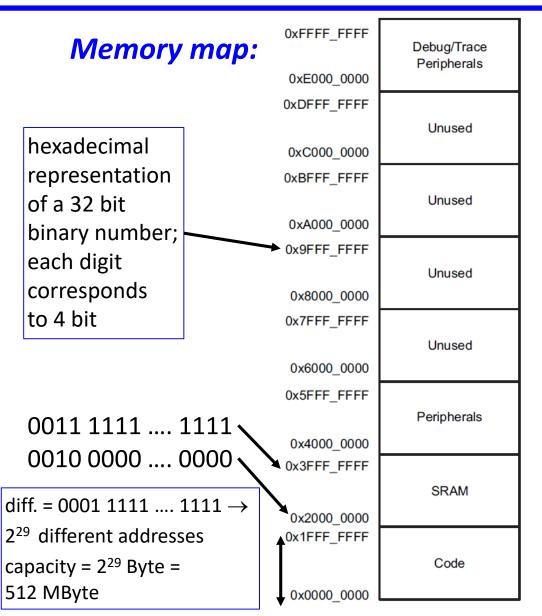

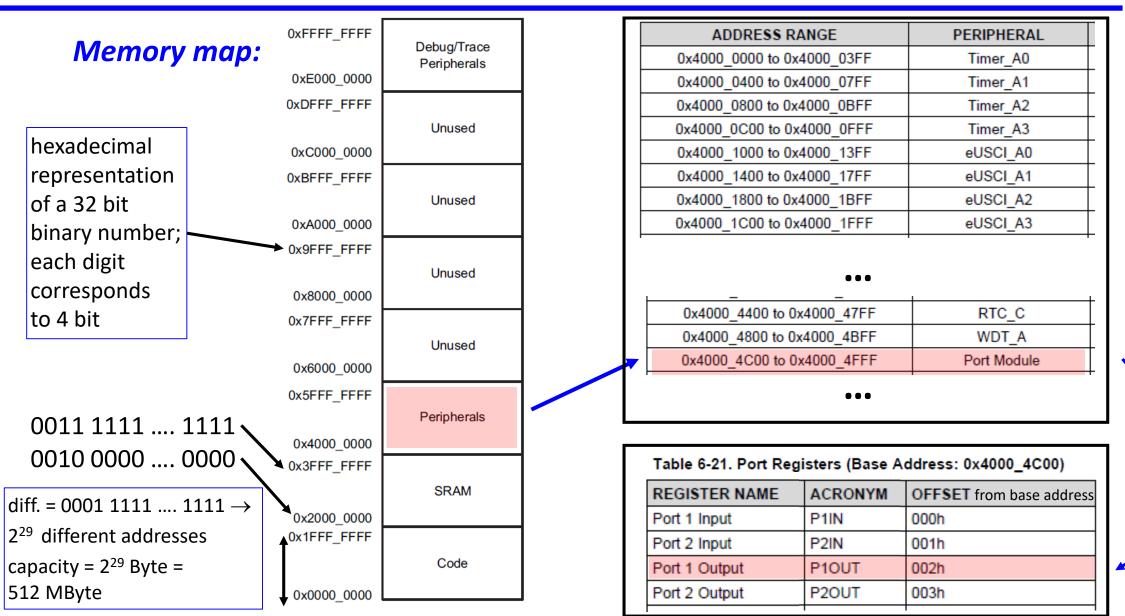

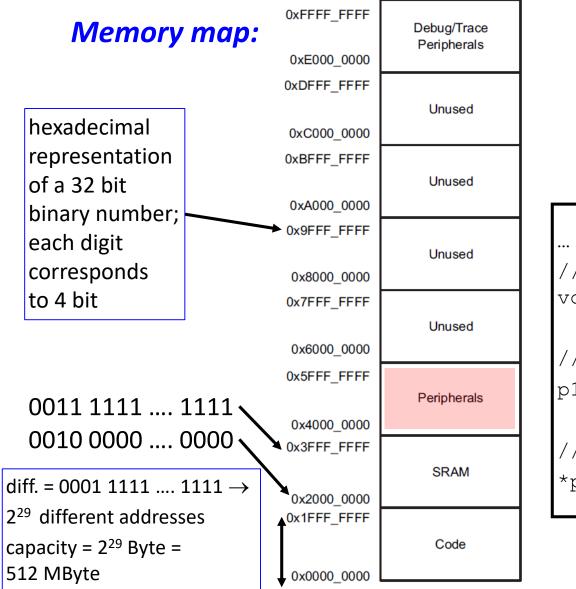

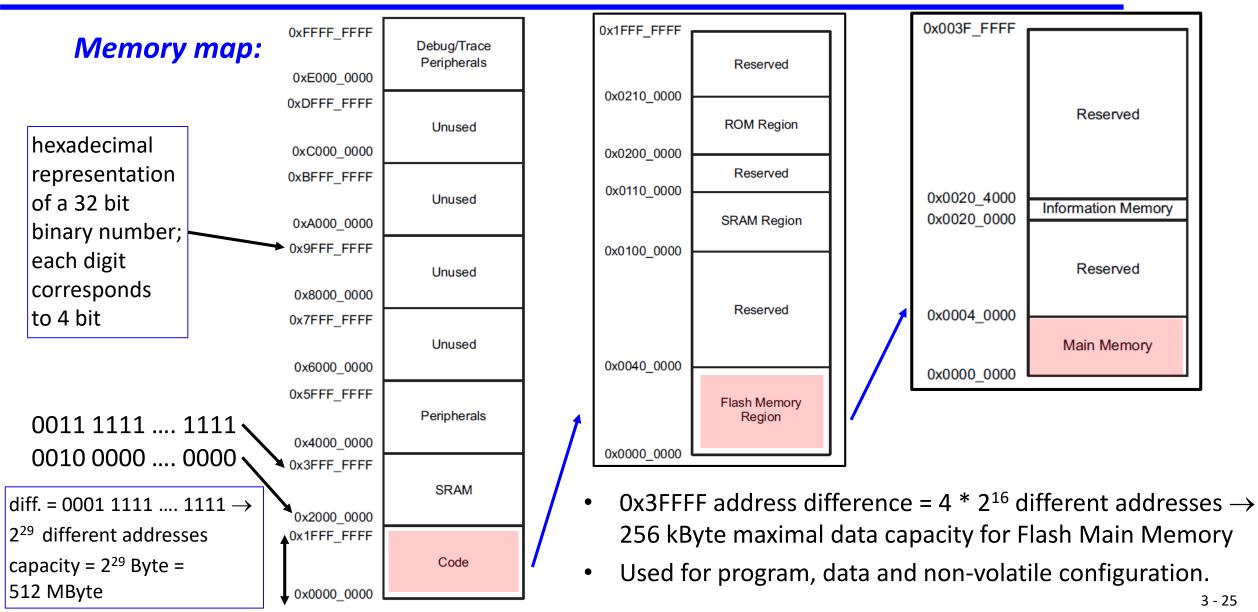

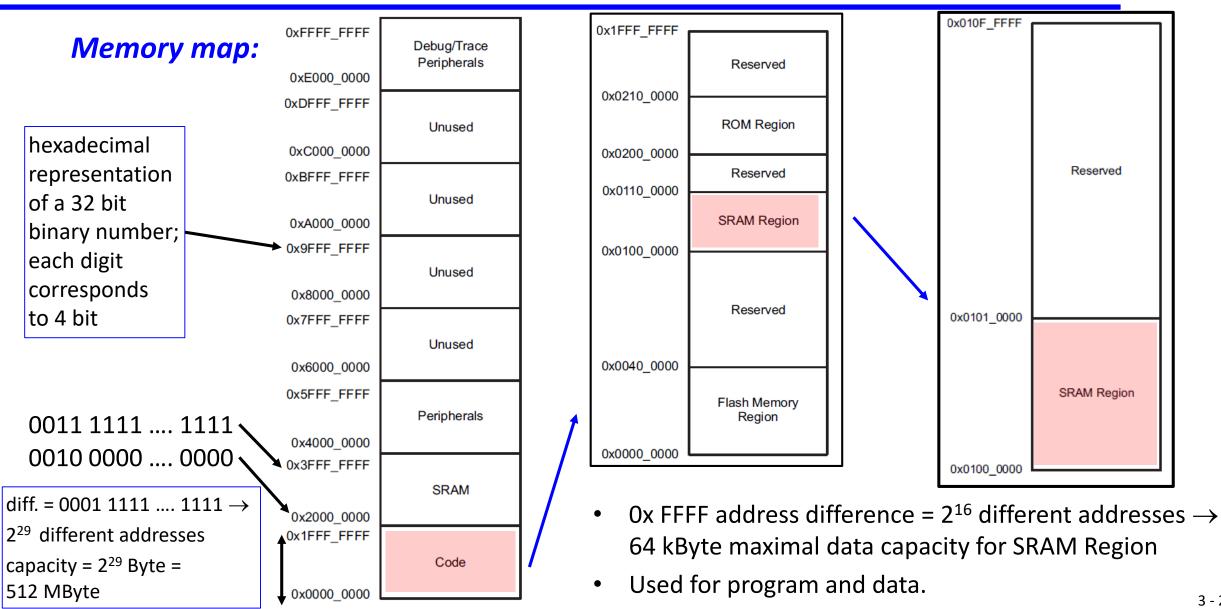

# Storage Memory Map

1

#### Available memory:

The processor used in the lab (MSP432P401R) has built in 256kB flash memory, 64kB SRAM and 32kB ROM (Read Only Memory).

#### Address space:

- The processor uses 32 bit addresses. Therefore, the addressable memory space is 4 GByte (= 2<sup>32</sup> Byte) as each memory location corresponds to 1 Byte.

- The address space is used to address the memories (reading and writing), to address the peripheral units, and to have access to debug and trace information (memory mapped microarchitecture).

- The address space is partitioned into zones, each one with a dedicated use. The following is a simplified description to introduce the basic concepts.

3 - 22

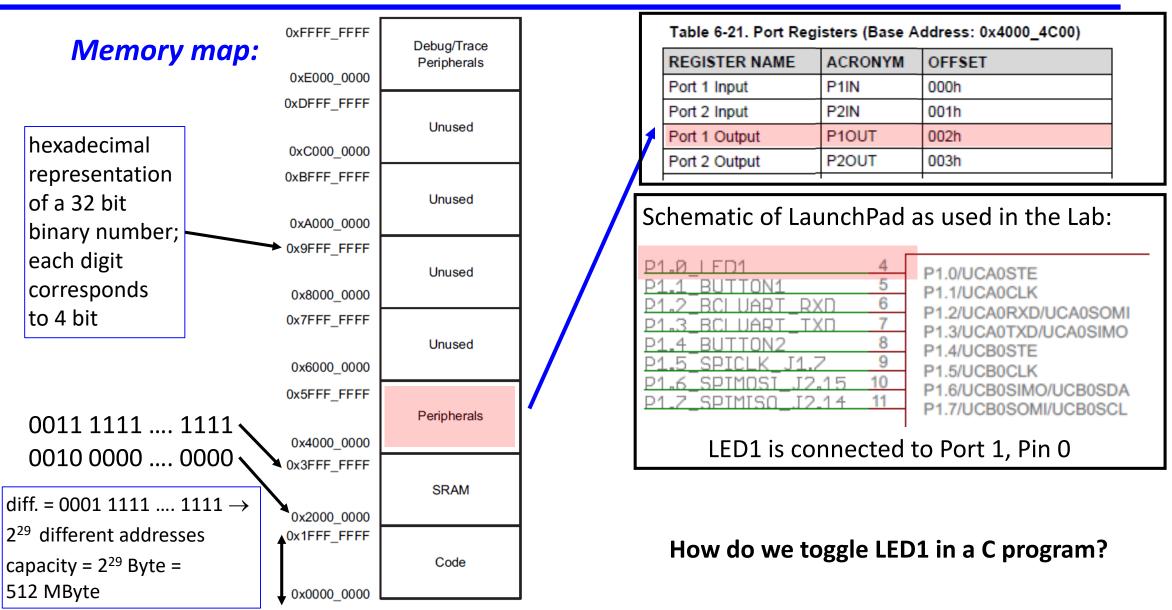

Many necessary elements are missing in the sketch below, in particular the configuration of the port (input or output, pull up or pull down resistors for input, drive strength for output). See lab session.

```

""

//declare plout as a pointer to an 8Bit integer

volatile uint8_t* plout;

//PlOUT should point to Port 1 where LED1 is connected

plout = (uint8_t*) 0x40004C02;

//Toggle Bit 0 (Signal to which LED1 is connected)

*plout = *plout ^ 0x01;

```

XOR

$\wedge$

### Input and Output

1

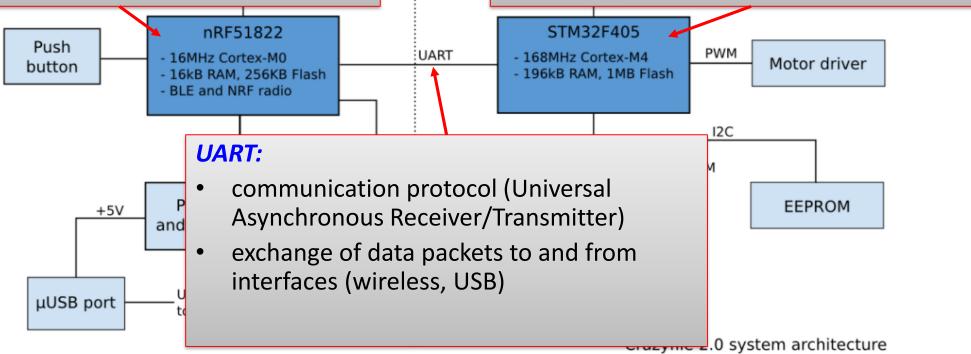

### **Device Communication**

Very often, a processor needs to *exchange information with other processors* or devices. To satisfy various needs, there exists many different *communication protocols*, such as

- UART (Universal Asynchronous Receiver-Transmitter)

- **SPI** (Serial Peripheral Interface Bus)

- I2C (Inter-Integrated Circuit)

- USB (Universal Serial Bus)

- As the principles are similar, we will just explain a representative of an asynchronous protocol (*UART*, no shared clock signal between sender and receiver) and one of a synchronous protocol (*SPI*, shared clock signal).

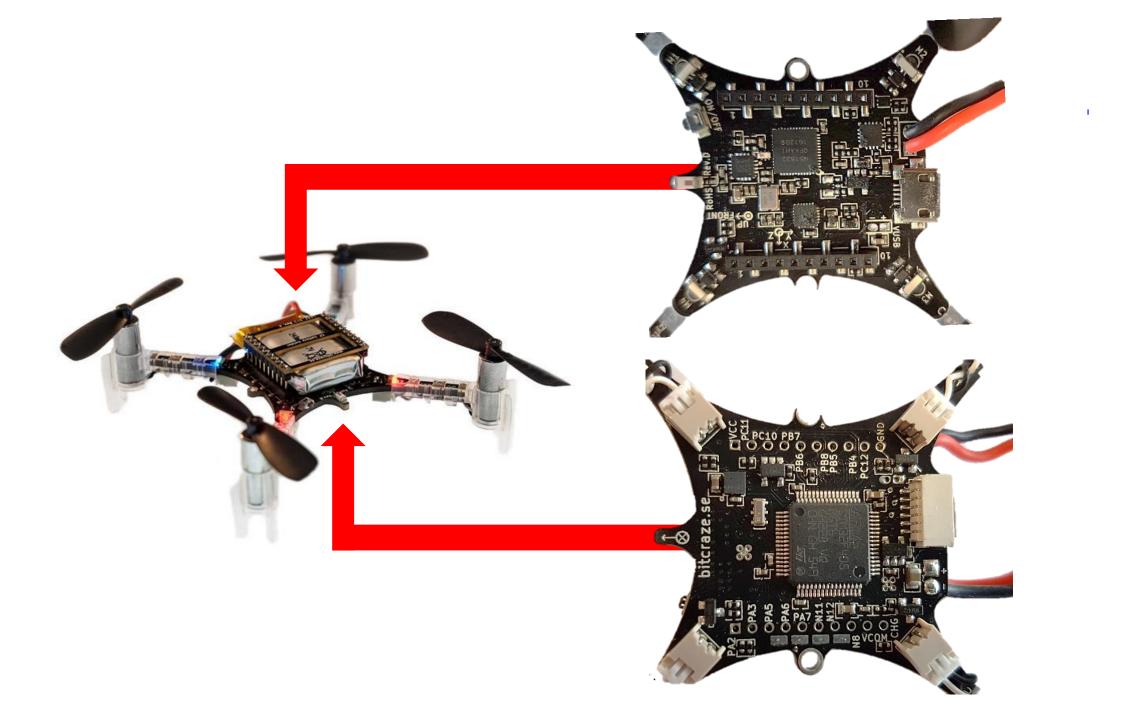

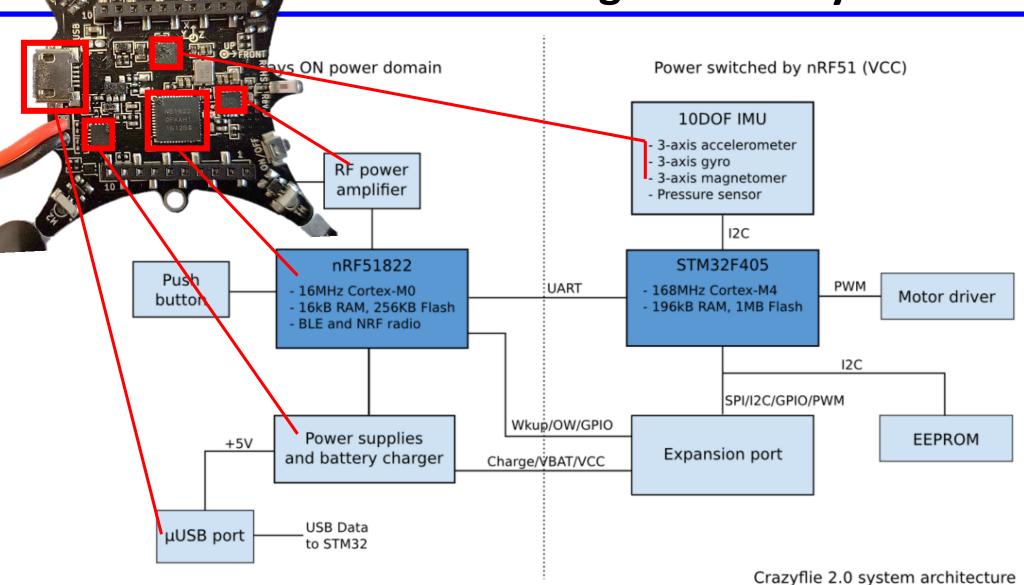

# **Remember?**

#### low power CPU

ullet

- enabling power to the rest of the system

- battery charging and voltage measurement

- wireless radio (boot and operate)

#### higher performance CPU

- sensor reading and motor control

- flight control

- telemetry (including the battery voltage)

- additional user development

- USB connection

# Input and Output UART Protocol

1

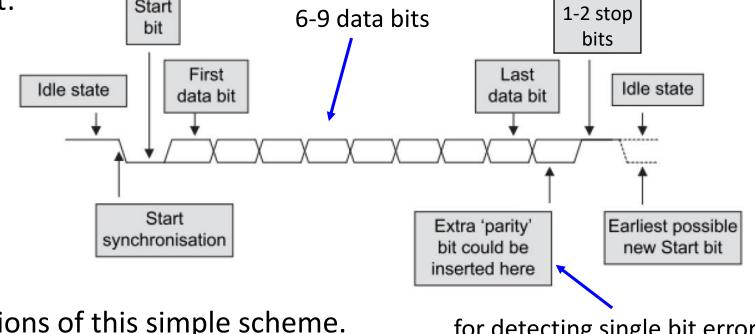

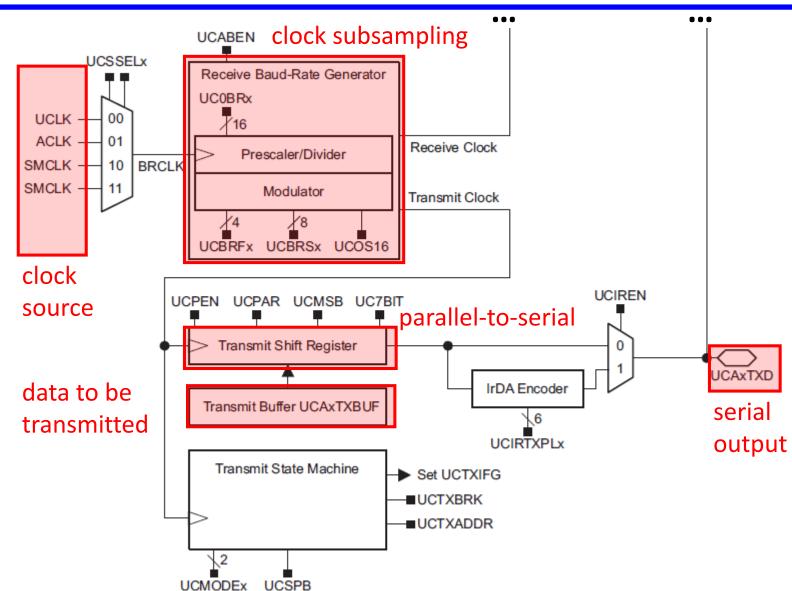

### UART

- *Serial communication* of bits via a single signal, i.e. UART provides parallel-to-serial and serial-to-parallel conversion.

- Sender and receiver need to *agree on the transmission rate*.

- Transmission of a serial packet starts with a start bit, followed by data bits and finalized using a stop bit: Start

There exist many variations of this simple scheme.

for detecting single bit errors

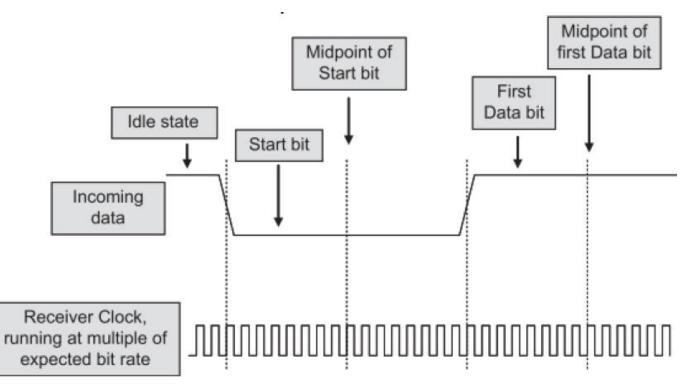

### UART

- The receiver runs an *internal clock* whose frequency is an exact multiple of the expected bit rate.

- When a *Start bit* is detected, a counter begins to count clock cycles e.g. 8 cycles until the midpoint of the anticipated Start bit is reached.

- The clock counter counts a further 16 cycles, to the middle of the first *Data bit*, and so on until the *Stop bit*.

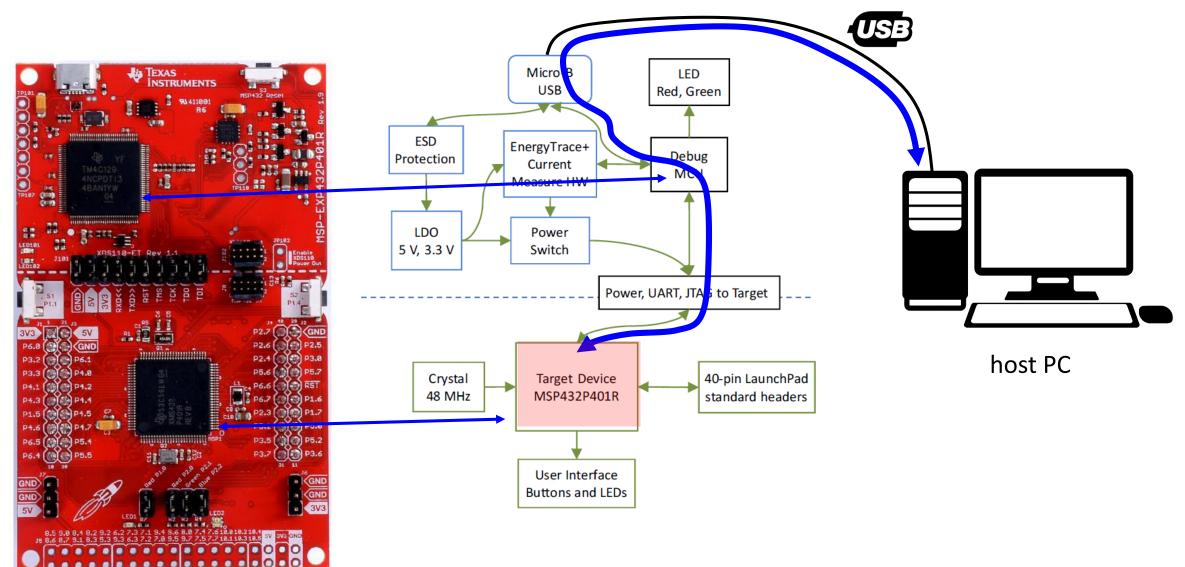

### UART with MSP432 (ES-Lab)

### UART with MSP432 (Lab)

# Input and Output Memory Mapped Device Access

1

### **Memory-Mapped Device Access**

#### eUSCI\_A0 Registers (Base Address: 0x4000\_1000)

| REGISTER NAME                   | OFFSET |

|---------------------------------|--------|

| eUSCI_A0 Control Word 0         | 00h    |

| eUSCI_A0 Control Word 1         | 02h    |

| eUSCI_A0 Baud Rate Control      | 06h    |

| eUSCI_A0 Modulation Control     | 08h    |

| eUSCI_A0 Status                 | 0Ah    |

| eUSCI_A0 Receive Buffer         | 0Ch    |

| eUSCI_A0 Transmit Buffer        | 0Eh    |

| eUSCI_A0 Auto Baud Rate Control | 10h    |

| eUSCI_A0 IrDA Control           | 12h    |

| eUSCI_A0 Interrupt Enable       | 1Ah    |

| eUSCI_A0 Interrupt Flag         | 1Ch    |

| eUSCI_A0 Interrupt Vector       | 1Eh    |

- Configuration of Transmitter and Receiver must match; otherwise, they can not communicate.

- Examples of configuration parameters:

- transmission rate (baud rate, i.e., symbols/s)

- LSB or MSB first

- number of bits per packet

- parity bit

- number of stop bits

- interrupt-based communication

- clock source

buffer for received bits and bits that should be transmitted

in our case: bit/s

## **Transmission Rate**

#### Clock subsampling:

The clock subsampling block is complex, as one tries to match a large set of transmission rates with a fixed input frequency.

#### Clock Source:

- SMCLK in the lab setup = 3MHz

- Quartz frequency = 48 MHz, is divided by 16 before connected to SMCLK

#### Example:

- Transmission rate 4800 bit/s

- 16 clock periods per bit (see 3-26)

- Subsampling factor = 3\*10^6 / (4.8\*10^3 \* 16) = 39.0625

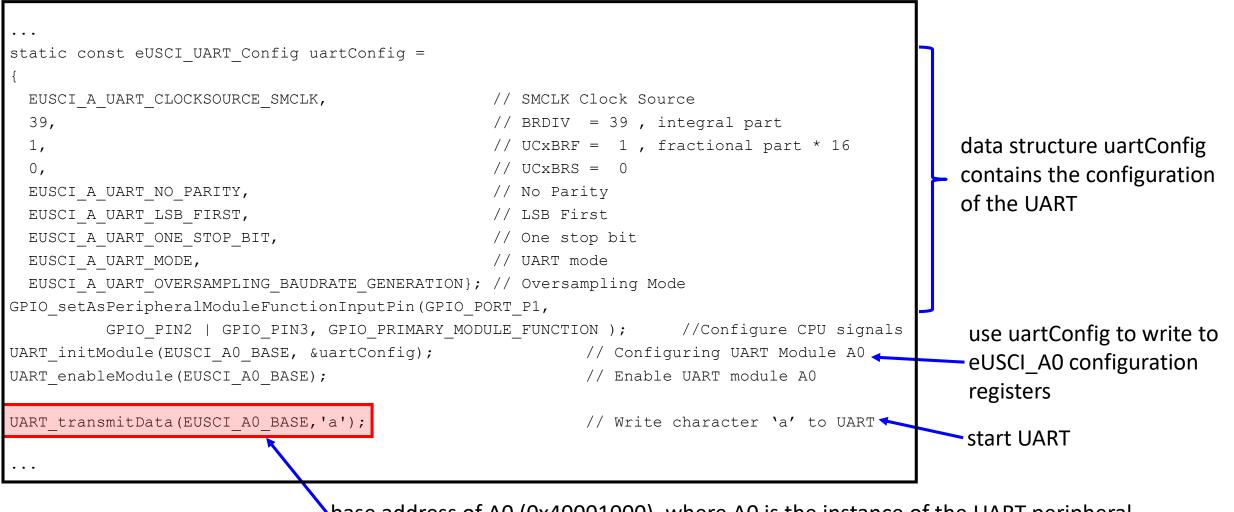

#### **Software Interface**

Part of C program that *prints a character to a UART* terminal on the host PC:

base address of A0 (0x40001000), where A0 is the instance of the UART peripheral

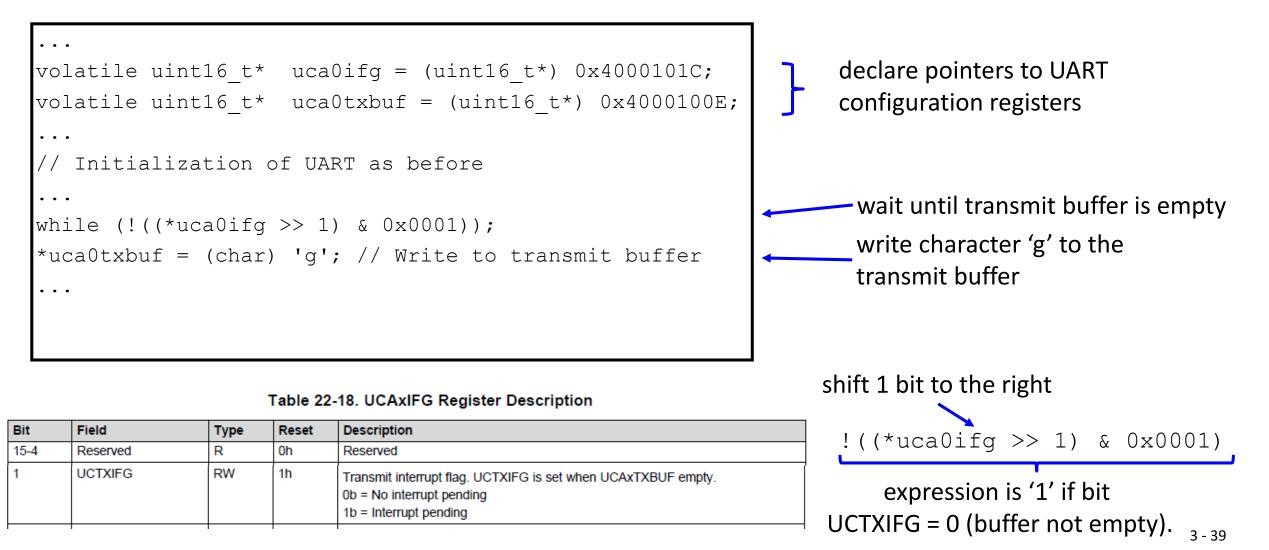

#### **Software Interface**

Replacing UART\_transmitData(EUSCI\_A0\_BASE,'a') by a *direct access to registers*:

## Input and Output SPI Protocol

1

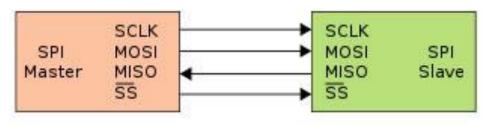

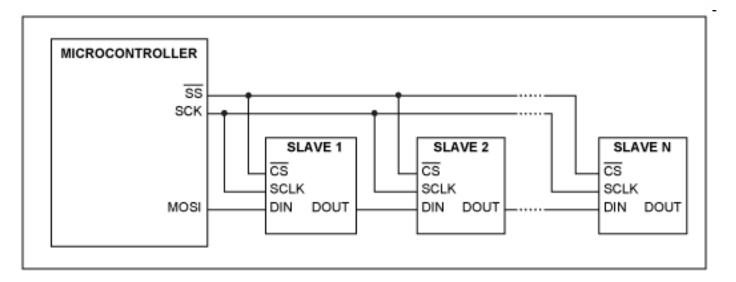

## **SPI (Serial Peripheral Interface Bus)**

- Typically communicate across short distances

- Characteristics:

- 4-wire synchronized (clocked) communications bus

- supports single master and multiple slaves

- always full-duplex: Communicates in both directions simultaneously

- multiple Mbps transmission speeds can be achieved

- transfer data in 4 to 16 bit serial packets

- Bus wiring:

- MOSI (Master Out Slave In) carries data out of master to slave

- MISO (Master In Slave Out) carries data out of slave to master

- Both MOSI and MISO are active during every transmission

- SS (or CS) signal to select each slave chip

- System clock SCLK produced by master to synchronize transfers

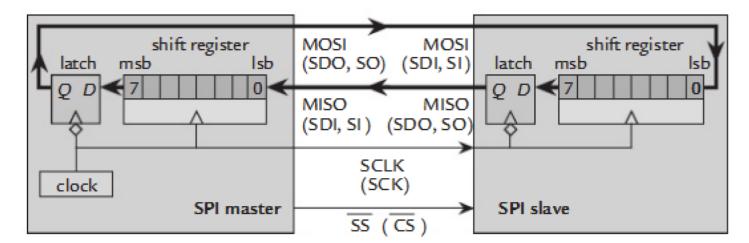

## **SPI (Serial Peripheral Interface Bus)**

#### More detailed circuit diagram:

details vary between different vendors and implementations

3 - 42

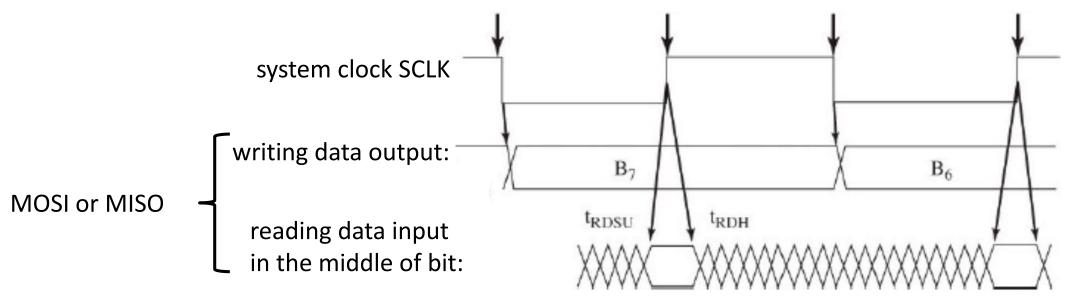

*Timing diagram:*

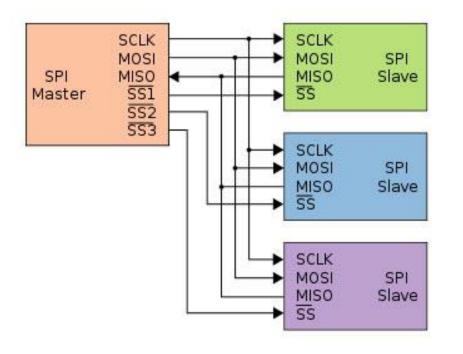

## **SPI (Serial Peripheral Interface Bus)**

#### Two examples of bus configurations:

#### Master and multiple independent slaves

$http://upload.wikimedia.org/wikipedia/commons/thumb/f/fc/SPI\_three\_slaves .svg/350px-SPI\_three\_slaves.svg.png$

Master and multiple daisy-chained

#### slaves

http://www.maxim-ic.com/appnotes.cfm/an\_pk/3947

#### Interrupts

#### Interrupts

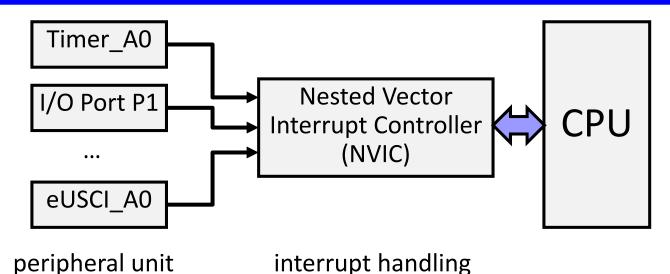

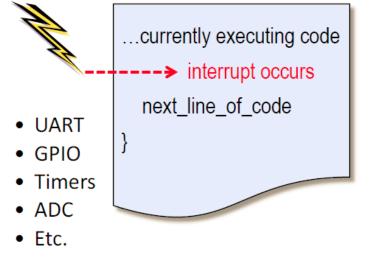

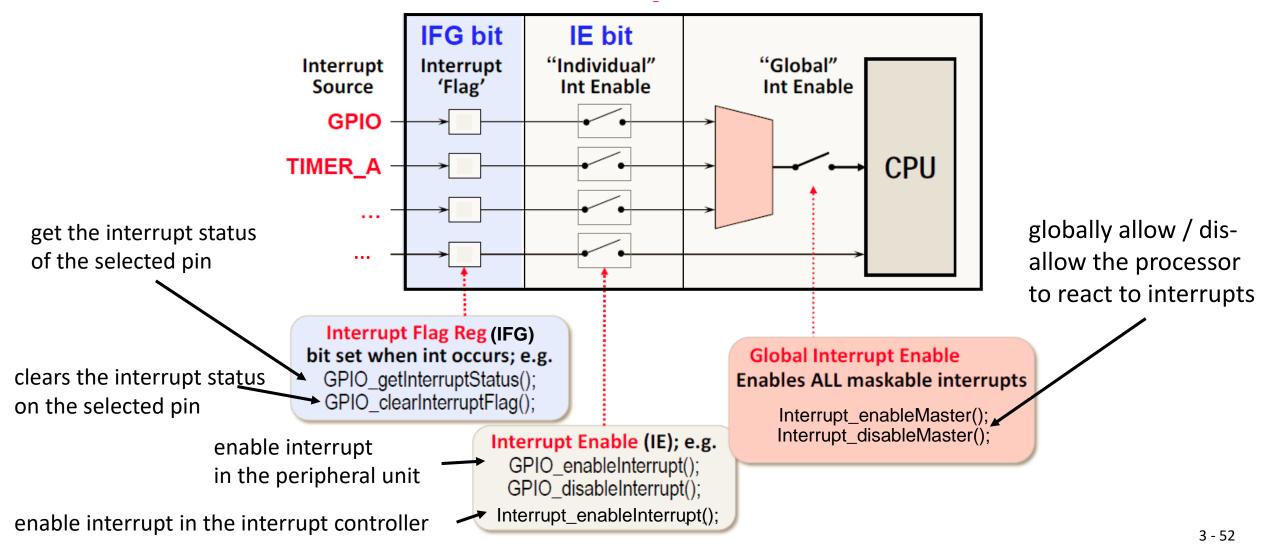

A hardware interrupt is an electronic alerting signal sent to the CPU from another component, either from an internal peripheral or from an external device.

The Nested Vector Interrupt Controller (NVIC) handles the processing of interrupts

#### Interrupts

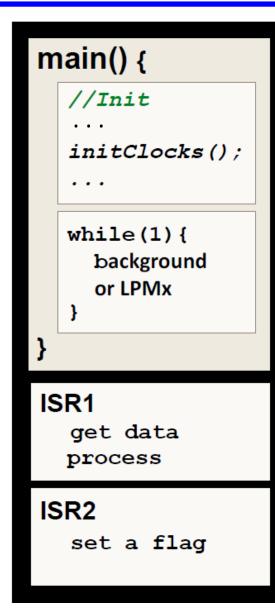

#### **System Initialization**

The beginning part of main() is usually dedicated to setting up your system

#### Background

- Most systems have an endless loop that runs 'forever' in the background

- In this case, 'Background' implies that it runs at a lower priority than 'Foreground'

- In MSP432 systems, the background loop often contains a Low Power Mode (LPMx) command – this sleeps the CPU/System until an interrupt event wakes it up

#### Foreground

- Interrupt Service Routine (ISR) runs in response to enabled hardware interrupt

- These events may change modes in Background such as waking the CPU out of low-power mode

- ISR's, by default, are not interruptible

- Some processing may be done in ISR, but it's usually best to keep them short

#### **Processing of an Interrupt (MSP432 ES-Lab)**

The vector interrupt controller (NVIC)

- enables and disables interrupts

- allows to individually and globally mask interrupts (disable reaction to interrupt), and

- registers *interrupt service routines* (ISR), sets the priority of interrupts.

Interrupt priorities are relevant if

- several interrupts happen at the same time

- the programmer does not mask interrupts in an interrupt service routine (ISR) and therefore, *preemption of an ISR* by another ISR may happen (interrupt nesting).

#### 1. An interrupt occurs

- Most peripherals can generate interrupts to provide status and information.

- Interrupts can also be generated from GPIO pins.

- When an interrupt signal is received, a corresponding bit is set in an IFG register.

- There is an such an IFG register for each interrupt source.

- As some interrupt sources are only on for a short duration, the CPU registers the interrupt signal internally.

#### 3. CPU/NVIC acknowledges interrupt by:

- current instruction completes

- saves return-to location on stack

- mask interrupts globally

- determines source of interrupt

- calls interrupt service routine (ISR)

#### 1. An interrupt occurs

# ...currently executing code interrupt occurs next\_line\_of\_code Timers ADC

• Etc.

#### 3. CPU/NVIC acknowledges interrupt by:

- current instruction completes

- saves return-to location on stack

- mask interrupts globally

- determines source of interrupt

- calls interrupt service routine (ISR)

#### 4. Interrupt Service Routine (ISR):

- save context of system

- run your interrupt's code

- restore context of system

- (automatically) un-mask interrupts and

- continue where it left off

#### **Detailed interrupt processing flow:**

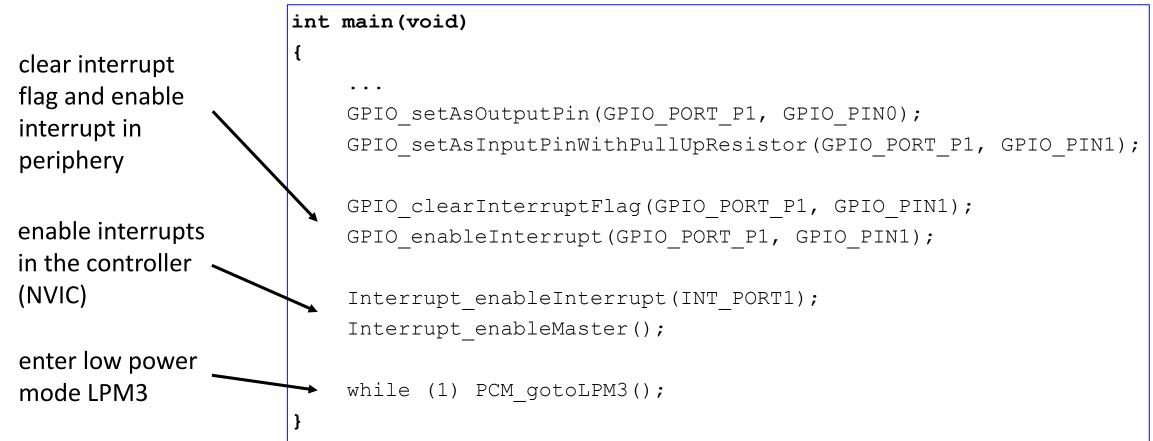

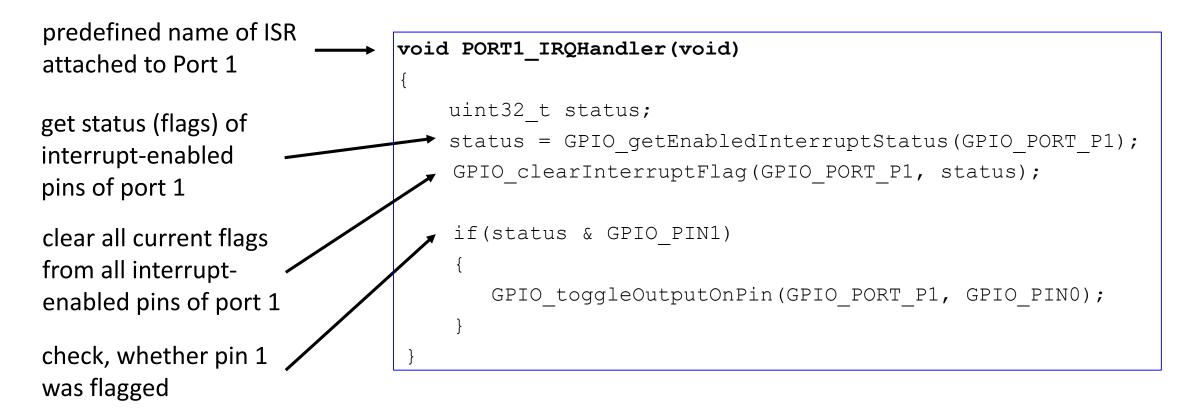

#### **Example: Interrupt Processing**

- Port 1, pin 1 (which has a switch connected to it) is configured as an *input* with interrupts enabled and port 1, pin 0 (which has an LED connected) is configured as an output.

- When the *switch is pressed*, the *LED output is toggled*.

#### **Example: Interrupt Processing**

- Port 1, pin 1 (which has a switch connected to it) is configured as an *input* with interrupts enabled and port 1, pin 0 (which has an LED connected) is configured as an output.

- When the switch is pressed, the LED output is toggled.

## **Polling vs. Interrupt**

functionality with polling: continuously get the signal at pin1 and detect falling edge

Similar

```

int main(void)

uint8 t new, old;

GPIO setAsOutputPin(GPIO_PORT_P1, GPIO_PIN0);

GPIO setAsInputPinWithPullUpResistor (GPIO PORT P1, GPIO PIN1);

old = GPIO getInputPinValue(GPIO PORT P1, GPIO PIN1);

while (1)

new = GPIO getInputPinValue(GPIO PORT P1, GPIO PIN1);

if (!new & old)

GPIO toggleOutputOnPin(GPIO PORT P1, GPIO PINO);

old = new;

```

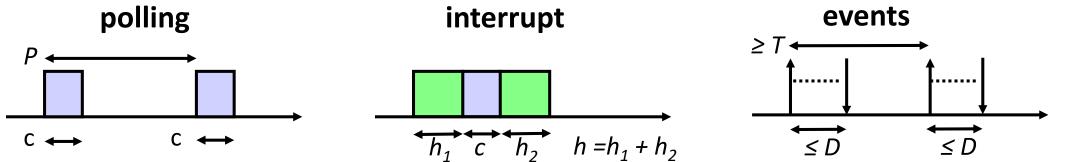

## **Polling vs. Interrupt**

#### What are advantages and disadvantages?

- We compare polling and interrupt based on the utilization of the CPU by using a simplified timing model.

- Definitions:

- *utilization u:* average percentage, the processor is busy

- *computation c:* processing time of handling the event

- overhead h: time overhead for handling the interrupt

- period P: polling period

- interarrival time T: minimal time between two events

- *deadline D:* maximal time between event arrival and finishing event processing with  $D \le T$ .

## **Polling vs. Interrupts**

For the following considerations, we suppose that the interarrival time between events is T. This makes the results a bit easier to understand.

Some relations for *interrupt-based* event processing :

- The average utilization is  $u_i = (h + c) / T$ .

- As we need at least h+c time to finish the processing of an event, we find the following constraint: h+c ≤ D ≤ T.

Some relations for *polling-based* event processing:

- The average utilization is  $u_p = c / P$ .

- We need at least time P+c to process an event that arrives shortly after a polling took place. The polling period P should be larger than c. Therefore, we find the following constraints: 2c ≤ c+P ≤ D ≤ T

#### **Polling vs. Interrupts**

**Design problem:** *D* and *T* are given by application requirements. *h* and *c* are given by the implementation. When to use interrupt and when polling when considering the resulting system utilization? What is the best value for the polling period P?

**Case 1**: If D < c + min(c, h) then event processing is not possible.

**Case 2**: If  $2c \le D \le h+c$  then only polling is possible. The maximal period P = D-c leads to the optimal utilization  $u_p = c / (D-c)$ .

**Case 3**: If  $h+c \le D < 2c$  then only interrupt is possible with utilization  $u_i = (h + c) / T$ . **Case 4**: If  $c + max(c, h) \le D$  then both are possible with  $u_p = c / (D-c)$  or  $u_i = (h + c) / T$ .

Interrupt gets better in comparison to polling, if the deadline D for processing interrupts gets smaller in comparison to the interarrival time T, if the overhead h gets smaller in comparison to the computation time c, or if the interarrival time of events is only lower bounded by T (as in this case polling executes unnecessarily).

#### **Clocks and Timers**

## Clocks and Timers Clocks

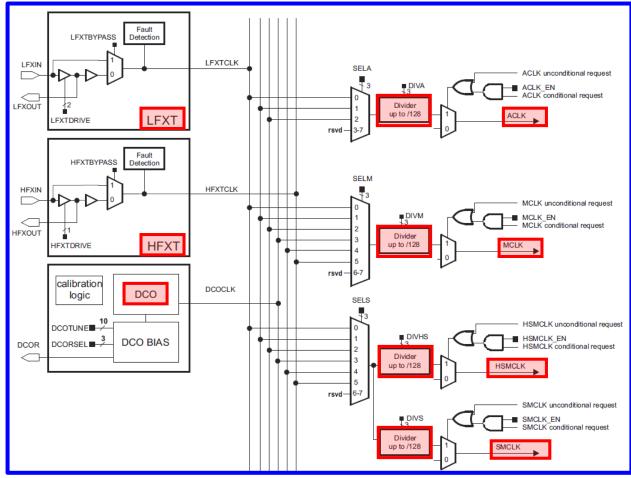

## Clocks

Microcontrollers usually have *many different clock sources* that have different

- frequency (relates to precision)

- energy consumption

- stability, e.g., crystal-controlled clock vs. digitally controlled oszillator

As an example, the MSP432 (ES-Lab) has the following *clock sources*:

|         | frequency | precision                   | current | comment          |

|---------|-----------|-----------------------------|---------|------------------|

| LFXTCLK | 32 kHz    | 0.0001% / °C<br>0.005% / °C | 150 nA  | external crystal |

| HFXTCLK | 48 MHz    | 0.0001% / °C<br>0.005% / °C | 550 μΑ  | external crystal |

| DCOCLK  | 3 MHz     | 0.025% / °C                 | N/A     | internal         |

| VLOCLK  | 9.4 kHz   | 0.1% / °C                   | 50 nA   | internal         |

| REFOCLK | 32 kHz    | 0.012% / °C                 | 0.6 μΑ  | internal         |

| MODCLK  | 25 MHz    | 0.02% / °C                  | 50 μΑ   | internal         |

| SYSOSC  | 5 MHz     | 0.03% / °C                  | 30 µA   | internal         |

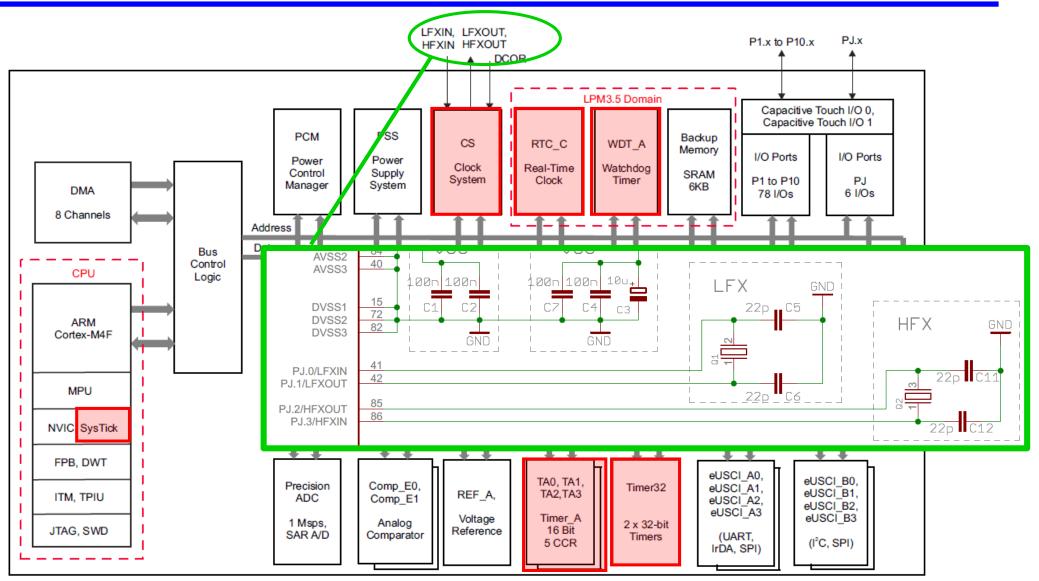

## Clocks and Timers MSP432 (ES-Lab)

Copyright © 2017 Texas Instruments Incorporated

#### Clocks and Timers MSP432 (ES-Lab)

Copyright © 2017 Texas Instruments Incorporated

## Clocks

From these basic clocks, *several internally available clock signals* are derived. They can be used for clocking peripheral units, the CPU, memory, and the various timers.

#### Example MSP432 (ES-Lab):

- only some of the clock generators are shown (LFXT, HFXT, DCO)

- dividers and clock sources for the internally available clock signals can be set by software

# Clocks and Timers Watchdog Timer

1

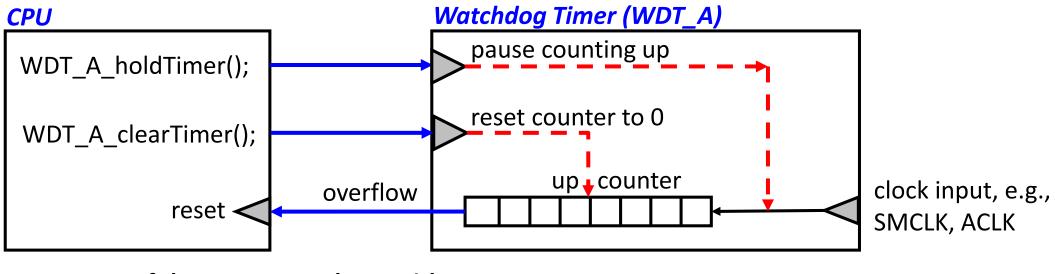

## Watchdog Timer

#### Watchdog Timers provide system fail-safety:

- If their counter ever rolls over (back to zero), they reset the processor. The goal here is to prevent your system from being inactive (deadlock) due to some unexpected fault.

- To prevent your system from continuously resetting itself, the counter should be reset at appropriate intervals.

If the count completes without a restart, the CPU is reset.

# Clocks and Timers System Tick

1

## SysTick MSP432 (ES-Lab)

- SysTick is a simple decrementing 24 bit counter that is part of the NVIC controller (Nested Vector Interrupt Controller). Its clock source is MCLK and it reloads to period-1 after reaching 0.

- It's a very simple timer, mainly used for periodic interrupts or measuring time.

```

int main(void) {

. . .

GPIO_setAsOutputPin(GPIO_PORT_P1, GPIO_PIN0);

SysTick enableModule();

if MCLK has a frequency of 3 MHz,

SysTick setPeriod(1500000);

an interrupt is generated every 0.5 s.

SysTick enableInterrupt();

Interrupt enableMaster();

while (1) PCM gotoLPMO(); — go to low power mode LPO after executing the ISR

void SysTick Handler(void) {

MAP GPIO toggleOutputOnPin(GPIO_PORT_P1, GPIO_PINO); }

```

## SysTick MSP432 (ES-Lab)

#### *Example for measuring the execution time* of some parts of a program:

```

int main(void) {

int32 t start, end, duration;

. . .

SysTick enableModule();

if MCLK has frequency of 3 MHz,

the counter rolls over every ~5.6 seconds

as (2^{24} / (3 \ 10^6) = 5.59

SysTick setPeriod(0x0100000);

SysTick disableInterrupt();

start = SysTick getValue();

... // part of the program whose duration is measured

the resolution of the duration is one

microsecond; the duration must not be

end = SysTick getValue();

duration = ((start - end) & 0x00FFFFFF)

longer than ~6 seconds; note the use of

modular arithmetic if end > start;

overhead for calling SysTick_getValue()

. . .

is not accounted for;

```

1

# Clocks and Timers Timer and PWM

1

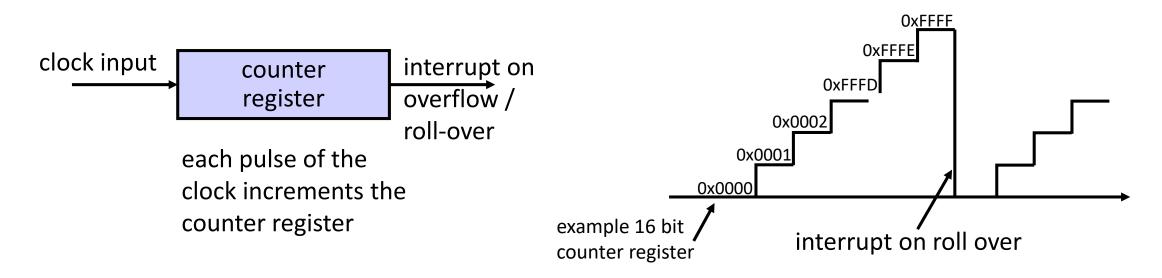

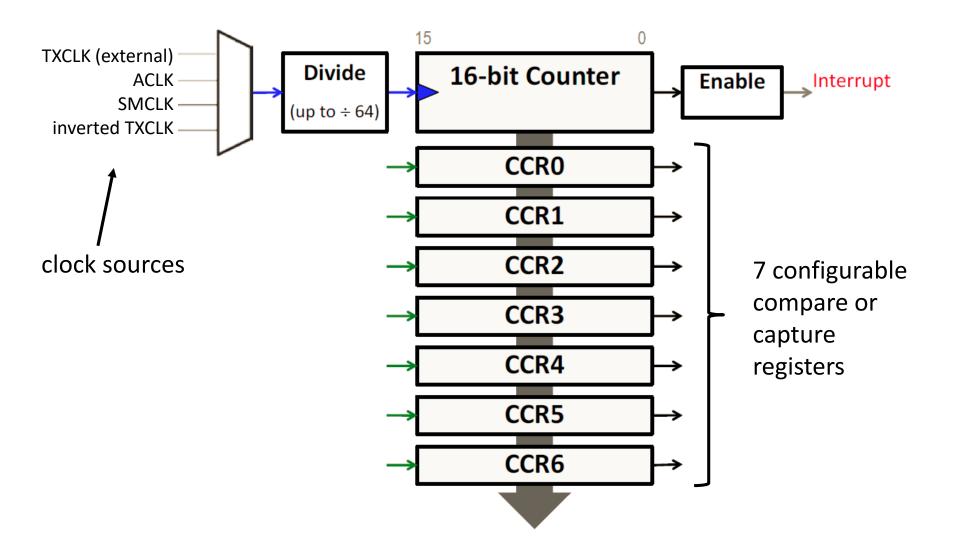

#### Timer

Usually, embedded microprocessors have several elaborate timers that allow to

- capture the current time or time differences, triggered by hardware or software events,

- generate interrupts when a *certain time is reached* (stop watch, timeout),

- generate interrupts when *counters overflow*,

- generate *periodic interrupts*, for example in order to periodically execute tasks,

- generate specific output signals, for example PWM (pulse width modulation).

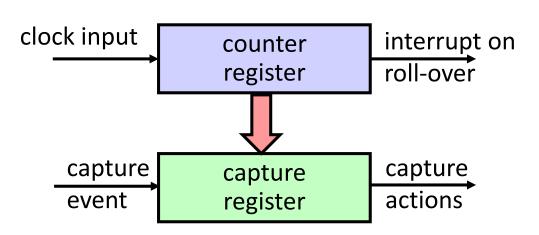

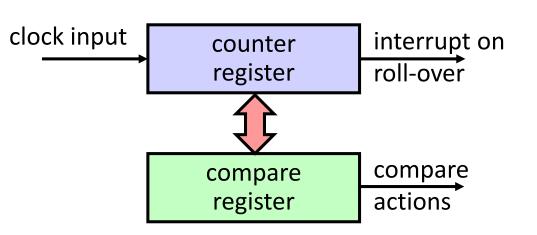

#### Timer

Typically, the mentioned functions are realized via *capture and compare registers*:

#### capture

- the value of the *compare register* can be set by software

- as soon as the values of the counter and compare register are equal, compare actions can be taken such as interrupt, signaling peripherals, changing pin values, resetting the counter register

- the value of *counter register* is stored in *capture register* at the time of the *capture event* (input signals, software)

- the value can be read by software

- at the time of the capture, further actions can be triggered (interrupt, signal)

compare

#### Timer

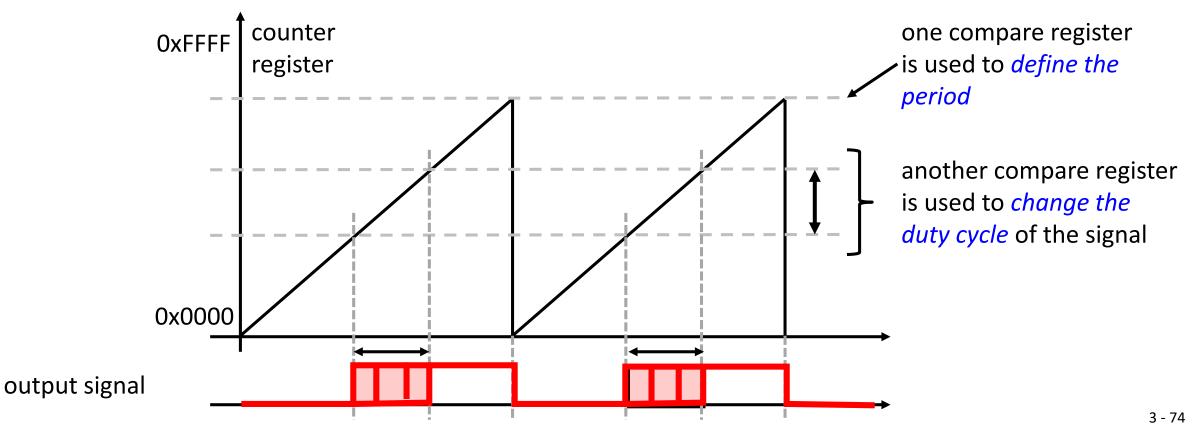

- Pulse Width Modulation (PWM) can be used to change the average power of a signal.

- The use case could be to change the speed of a motor or to modulate the light intensity of an LED.

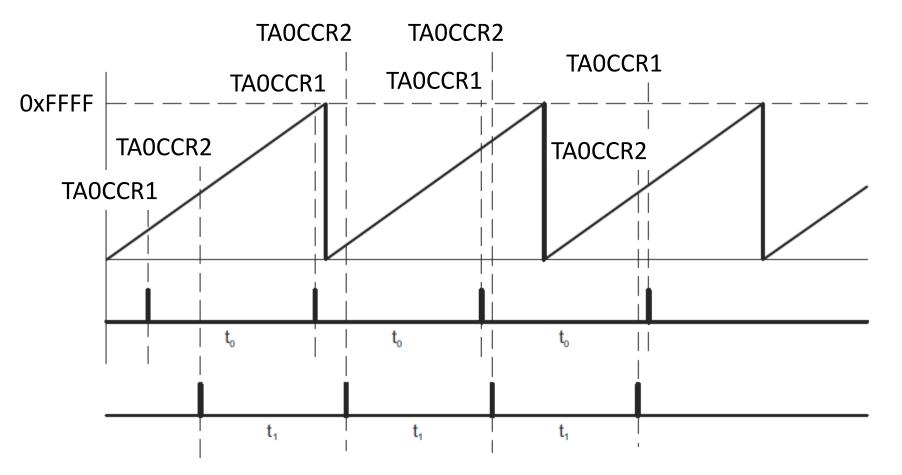

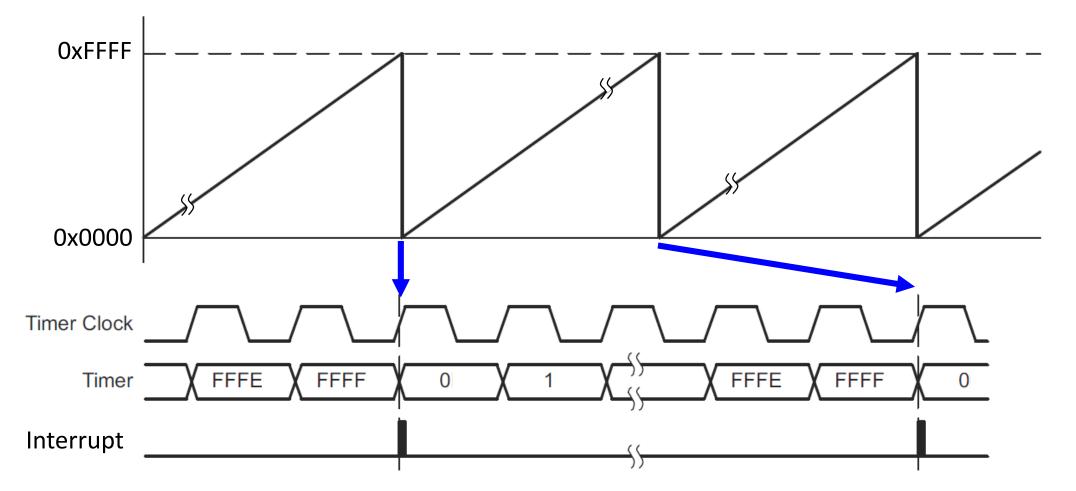

**Example:** Configure Timer in "continuous mode". Goal: generate periodic interrupts.

**Example:** Configure Timer in "continuous mode". Goal: generate periodic interrupts.

**Example:** Configure Timer in "continuous mode". *Goal:* generate periodic interrupts, **but** with configurable periods.

```

int main(void) {

. .

const Timer A ContinuousModeConfig continuousModeConfig = {

TIMER A CLOCKSOURCE ACLK,

clock source is ACLK (32.768 kHz);

TIMER A CLOCKSOURCE DIVIDER 1,

so far,

divider is 1 (count frequency 32.768 kHz);

TIMER_A_TAIE_INTERRUPT_DISABLE,

nothing

no interrupt on roll-over;

TIMER A DO CLEAR };

happens

configure continuous mode

only the

of timer instance A0

counter is

Timer A configureContinuousMode (TIMER A0 BASE, &continuousModeConfig);

running

Timer A startCounter (TIMER A0 BASE, TIMER A CONTINUOUS MODE);

. . .

start counter A0 in

while(1) PCM gotoLPM0(); }

continuous mode

```

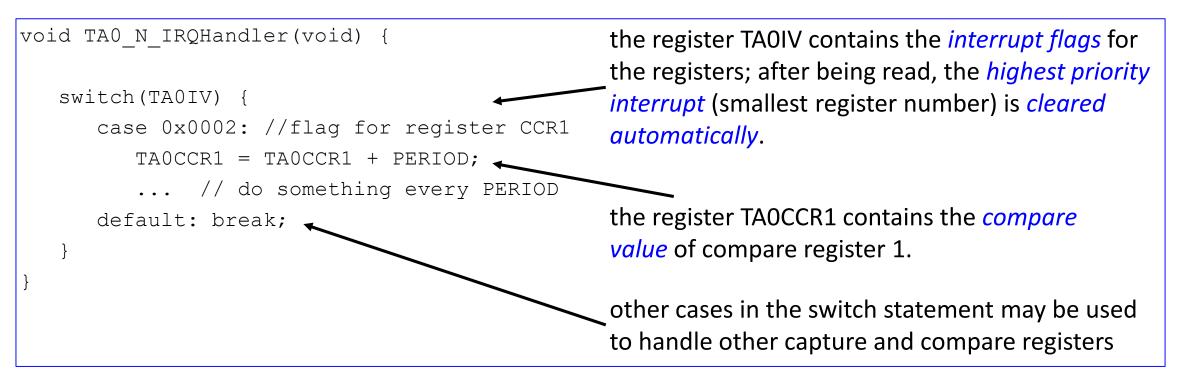

#### Example:

- For a *periodic interrupt*, we need to add a *compare register and an ISR*.

- The following code should be added as a definition:

#define PERIOD 32768

The following code should be added to main():

```

const Timer_A_CompareModeConfig compareModeConfig = {

TIMER_A_CAPTURECOMPARE_REGISTER_1,

TIMER_A_CAPTURECOMPARE_INTERRUPT_ENABLE,

0,

PERIOD};

...

Timer_A_initCompare(TIMER_A0_BASE, &compareModeConfig);

Timer_A_enableCaptureCompareInterrupt(TIMER_A0_BASE, TIMER_A_CAPTURECOMPARE_REGISTER_1);

Interrupt_enableInterrupt(INT_TA0_N);

Interrupt_enableMaster();

```

#### Example:

- For a *periodic interrupt*, we need to add a *compare register and an ISR*.

- The following Interrupt Service Routine (ISR) should be added. It is called if one of the capture/compare registers CCR1 ... CCR6 raises an interrupt

**Example:** This principle can be used to generate several periodic interrupts with one timer.