# Embedded Systems Autumn 2020

Intermediate Test - Solution Lothar Thiele 28.10.2020

# **Preliminary Comments**

- The test will not be graded by us. The purpose of the test is to provide you with some means to evaluate the state of your knowledge.

- It is highly advised, that you solve the questions under exam conditions. You should print the intermediate test. The exam is "open book", therefore, you can use some of the material from the lectures, exercises and labs. Please note that during the exam, you can only use printed material and a pocket calculator.

- The questions are taken from old exams. The time allocated for these questions would be about 45 minutes. To pass, you should achieve about 40%-50% of the maximal points.

- I will explain the solutions and answer questions during the exercise session on Wednesday, November 4.

### Short Questions

(8 points)

Answer the following questions for the MSP-432 processor:

(a) (3 points) A system uses UART to transmit data, with the following configuration: the baud rate is 115 200 bits/s, 1 start bit, 2 stop bits, 7 data bits and 1 parity bit. How much time is needed to transmit 240 KB of data (1 KB = 1024 bytes)?

# Sample solution:

Symbols transmitted with overhead:  $\lceil 240 \times 1024 \times 8 \times \frac{11}{7} \rceil = 3\,089\,555\,\text{bit}$ Time to transmit:  $3\,089\,555\,\text{bit}/115\,200\,\frac{\text{bit}}{\text{s}} = 26.82\,\text{s}.$

(b) (2 points) How many bytes can be written in a block of memory accessed using byteaddresses 0x3000\_0000 through 0x308F\_FFFF?

### Sample solution:

<code>0x308F\_FFFF</code> – <code>0x3000\_0000</code> + 1 = <code>0x008F\_FFFF</code> + 1 = <code>0x0090\_0000</code> There are  $9 \times 2^{20}$  addresses, which means 9 Megabytes of memory.

(c) (3 points) The following function returns the value that has been read from the appropriate GPIO port (pin 7 being the MSB).

uint8\_t GPIO\_getInputPortValue(uint\_fast8\_t selectedPort); Pins 0 through 7 of GPIO port PORT1 are equipped with buttons with pull-up resistors (when the button is not pressed, the GPIO is connected to the supply voltage; when the button is pressed, the GPIO is connected to the ground). If only buttons connected to pins 2 and 7 of PORT1 are pressed, what value will variable uint8\_t kk have after the following line of code is executed?

uint8\_t kk = GPI0\_getInputPortValue(PORT1) & 0x3C; Hint: & is the logical AND operator.

### Sample solution:

As pull-up resistors are used, a pushed button yields a 0, while a released one yields 1. We therefore have:

kk = 0b0111\_1011 AND 0b0011\_1100 = 0b0011\_1000 = 0x38

#### (9 points)

#### **Pulse Width Modulation**

A code snippet is shown below, which shows the configuration of timer A1 for generating Pulse Width Modulation (PWM) signals on the MSP-432. Based on this code, answer the following questions.

```

1 /* Timer_A1 up mode configuration parameters */

2 const Timer_A_UpModeConfig upConfigA1 =

3 {

// SMCLK clock source runs at 3MHz

TIMER_A_CLOCKSOURCE_SMCLK,

4

// SMCLK divider set to 3

TIMER_A_CLOCKSOURCE_DIVIDER_3,

5

// Value in CCR0

6

71,

TIMER_A_TAIE_INTERRUPT_DISABLE,

// Disable Timer interrupt

7

TIMER_A_CCIE_CCR0_INTERRUPT_DISABLE, // Disable CCR0 interrupt

8

// Clear value

TIMER_A_DO_CLEAR

9

10 };

11

12 /* Timer_A1 compare configuration parameters */

13 Timer_A_CompareModeConfig compareConfigA1 =

14 {

15 TIMER_A_CAPTURECOMPARE_REGISTER_1,

// Use CCR1 as compare register

16 TIMER_A_CAPTURECOMPARE_INTERRUPT_DISABLE, // Disable CCR interrupt

17 TIMER_A_OUTPUTMODE_TOGGLE_RESET, // Toggle-reset output mode

// Compare value (CCR1)

18 60

19 };

20

21 /* Configure the compare functionality of Timer_A1 */

22 Timer_A_initCompare(TIMER_A1_BASE, &compareConfigA1);

23 /* Configure Timer_A1 for Up Mode */

24 Timer_A_configureUpMode(TIMER_A1_BASE, &upConfigA1);

25 /* Start counter of Timer_A1 */

26 Timer_A_startCounter(TIMER_A1_BASE, TIMER_A_UP_MODE);

```

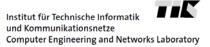

(a) (3 points) Calculate the period of timer A1, in microseconds. Show the steps of your calculation.

### Sample solution:

The period is  $(71+1) \times \frac{3}{3 \times 10^6}\, {\rm s} = 72\,\mu {\rm s}$

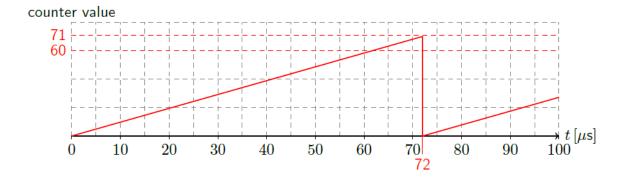

(b) (3 points) Calculate the PWM duty-cycle (the ratio of time the PWM signal is high), in percent. Show the steps of your calculation.

### Sample solution:

The ON-time is  $\frac{71+1-60-1}{71+1} = 15.28 \%$

(c) (3 points) Sketch the evolution of the counter value of timer A1, as well as the PWM output signal, from time  $0 \mu s$  to time  $10 \mu s$ . Indicate where the output signal toggles. Assume that the value of the counter is zero at time  $0 \mu s$ .

#### Interrupts

#### (maximal 7 points)

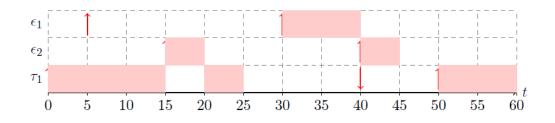

A system consists of one task  $\tau_1$  and two interrupts  $\epsilon_1$  and  $\epsilon_2$ , with the following parameters. Task  $\tau_1$  has period  $P_{\tau_1} = 50$ , execution time  $C_{\tau_1} = 20$ , initial phase  $\phi_{\tau_1} = 0$ , and relative deadline  $D_{\tau_1} = 40$ . Interrupt  $\epsilon_1$  has a minimal inter-arrival time  $T_{\epsilon_1} = 20$ , and execution time  $C_{\epsilon_1} = 7$ . Interrupt  $\epsilon_2$  has a minimal inter-arrival time  $T_{\epsilon_2} = 15$ , and execution time  $C_{\epsilon_1} = 2$ . For both interrupts, the overhead is h = 3. From the moment an instance of task  $\tau_1$  is released, until it finishes execution, interrupt  $\epsilon_1$  is ignored, while interrupt  $\epsilon_2$  is serviced immediately whenever it appears. For this system, answer the following questions.

(a) (3 points) Assuming interrupt  $\epsilon_1$  arrives at times 5 and 30, and interrupt  $\epsilon_2$  arrives at times 15 and 40, draw the execution of the task and interrupts from time 0 to time 60.

#### Sample solution:

(b) (4 points) What is the minimal inter-arrival time for interrupt  $\epsilon_2$ , such that task  $\tau_1$  can never miss its deadline?

Hint: Search for the worst-case scenario with regards to the arrival of interrupts.

#### Sample solution:

The worst case arrival time of interrupt  $\epsilon_1$  is just before 0. If interrupt  $\epsilon_2$  preempts task  $\tau_1 x$  times, we have:  $C_{\epsilon_1} + h + x \cdot (C_{\epsilon_2} + h) + C_{\tau_1} \leq D_{\tau_1}$ , which gives  $x \leq 2$ . This means,  $T_{\epsilon_2} = 20$  is the minimal inter-arrival time such that task  $\tau_1$  can not miss its deadline.

# Cyclic-Executive Scheduling

(8 points)

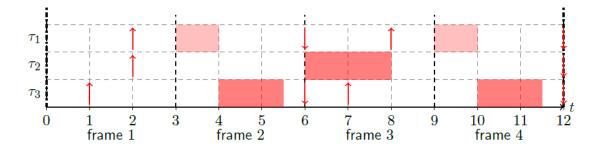

Cyclic-executive scheduling with a period P = 12 and a frame length f = 3 is used to schedule the task-set given in Table 1. Note that "frame 1" is the first frame of each period.

| Task    | Period | Deadline | Phase | Execution Time | Frames |

|---------|--------|----------|-------|----------------|--------|

| $	au_1$ |        | 4        |       | 1              | 2, 4   |

| $	au_2$ | 12     | 10       | 2     | 2              |        |

| $	au_3$ | 6      | 5        | 1     | 1.5            |        |

Table 1: A task set

(a) (4 points) Determine one feasible assignment of tasks  $\tau_2$  and  $\tau_3$  to frames, construct the schedule for one period P and illustrate it graphically.

### Sample solution:

One possible assignment is shown

(b) (4 points) Determine the period of task  $\tau_1$  and its minimal possible phase, if the task is executed in frames 2 and 4.

### Sample solution:

The period of task  $\tau_1$  is 6, as it occurs twice in 12 time units. The minimal solution for the initial phase for task  $\tau_1$  is 2.

# (5 points)

# Earliest Deadline First, Online

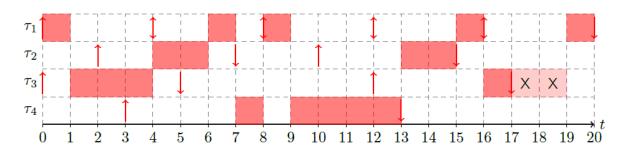

We have a task-set with four tasks whose jobs arrive aperiodically, and the system schedules them with Earliest Deadline First. Details on the task set, and the release times of tasks are given in Table 4.

|                   | $	au_1$         | $	au_2$ | $	au_3$ | $	au_4$ |

|-------------------|-----------------|---------|---------|---------|

| Release Times     | 0, 4, 8, 12, 16 | 2, 10   | 0, 12   | 3       |

| Relative Deadline | 4               | 5       | 5       | 10      |

| Execution Time    | 1               | 2       | 3       | 5       |

Table 4: A task set

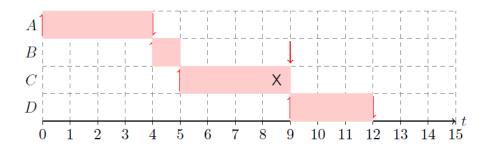

(a) (4 points) Construct a schedule according to EDF, and illustrate it graphically from

(b) (1 point) Based on your result in part (a), in the online scheduling case, at what time can the system detect that a deadline violation will happen? Online scheduling assumes that the system does not know the arrival time of jobs, until they actually arrive.

# Sample solution:

At time 12, the deadline miss at time 17 is detected.

time 0 to time 20. Indicate any deadline misses.

### (maximal 6 points)

# Earliest Deadline First (EDF\*)

Four jobs A, B, C, and D, execute with the following precedence constraints:  $A \rightarrow B$ ,  $A \rightarrow C$ ,  $B \rightarrow D$ , and  $C \rightarrow D$ . More details about the jobs are given in Table 2

Table 2: A task set

|                | A  | B  | C | D  |

|----------------|----|----|---|----|

| Release Time   | 0  | 0  | 5 | 0  |

| Deadline       | 12 | 12 | 8 | 12 |

| Execution Time | 4  | 1  | 4 | 3  |

(a) (4 points) Modify the release times and deadlines of jobs according to the EDF\* algorithm, such that EDF can be used for scheduling without breaking any precedence constrains.

# Sample solution:

|                       | A | B | C | D  |

|-----------------------|---|---|---|----|

| Modified Release Time | 0 | 4 | 5 | 9  |

| Modified Deadline     | 4 | 9 | 8 | 12 |

(b) (2 points) Construct a schedule according to EDF\*, and illustrate it graphically. Note any jobs that miss their deadline.

# Sample solution: