### Low-Power System Design

227-0781-00L Fall Semester 2019 Jan Beutel

## Plan for Today

- Recap logistics if anyone is new

- Lecture

- Reading/Writing Seminar

- Hands-on Design Project

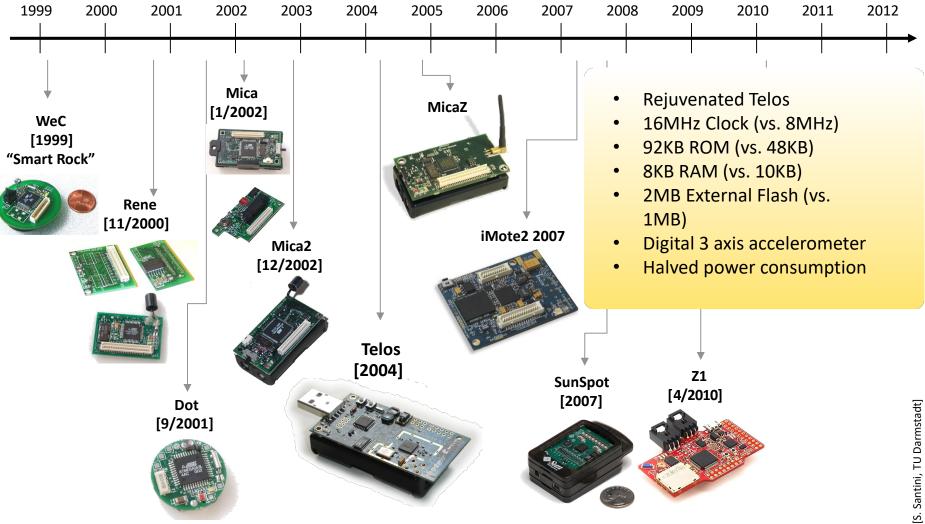

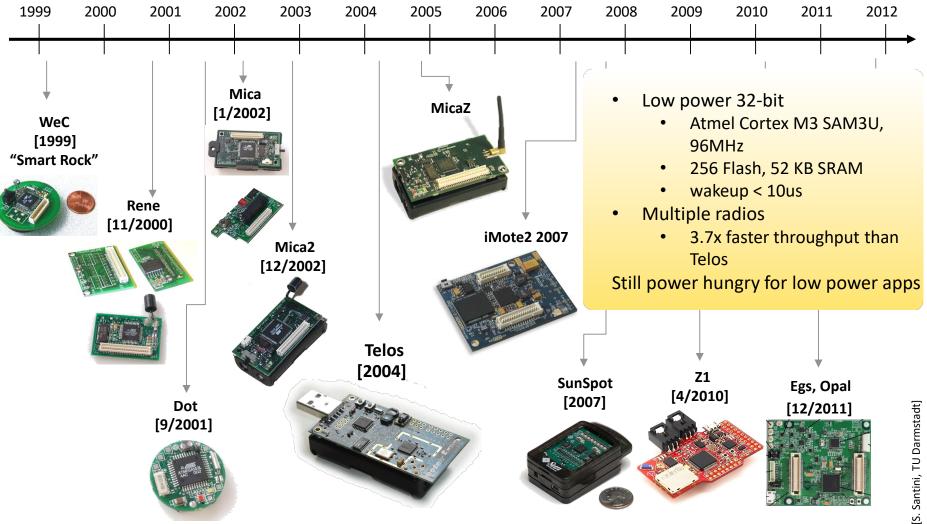

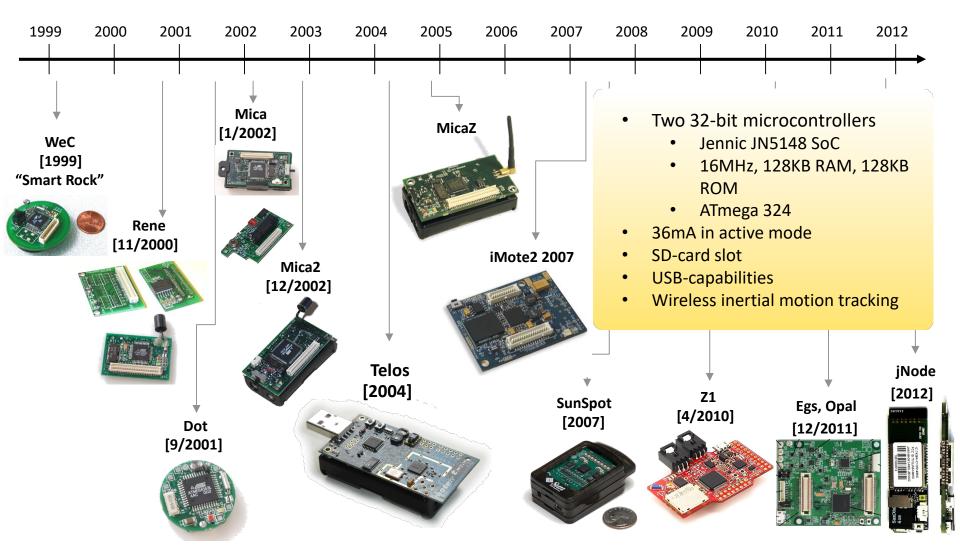

- Evolution of low-power embedded sensing systems

- LP system architectures processor systems

- Application example

- PermaSense Project Architecture

Low-Power System Design

### **COURSE LOGISTICS**

### **Course Components**

- Goals of LPSD

- Introduction to the state-of-the-art in research

- Empowering students to ask relevant questions and develop ideas critically

- Enable students to work on a research project of publishable quality

- Components

- Up front lecture with slides (please make it interactive, ask questions)

- Reading and writing seminar

- Hands-on practical work, design project

### **Course Resources**

• Online course web page

https://www.tec.ee.ethz.ch/education/lectures/low-power-systemdesign.html

- Syllabus

- Reading material

- Assignments

- Links to further resources

- Updates to material as we progress

- Riot chat room for reading seminar: <u>#lpsd:matrix.ee.ethz.ch</u>

- Submitting reviews

- Discussion

- Sharing of other related papers, interesting stuff

- Questions/Answers

- In case of questions: janbeutel@ethz.ch

### Lecture Schedule

| Week | Date       | Lecture Wednesday 10-12h                                   | Lab Exercises Wednesday 13-15h          |

|------|------------|------------------------------------------------------------|-----------------------------------------|

| 1    | 18.09.2019 | Lecture 1 - Course Introduction, Definitions, Metrics      | Reading/Writing Seminar Introduction    |

| 2    | 25.09.2019 | Lecture 2 - LP System Architectures                        | Lab 1                                   |

| 3    | 02.10.2019 | Lecture 3 – LP System Architectures                        | Lab 2                                   |

| 4    | 09.10.2019 | No Lecture - Reading Seminar only                          | Lab 3                                   |

| 5    | 16.10.2019 | No Lecture - Reading Seminar only                          | Lab 4                                   |

| 6    | 23.10.2019 | Lecture 4 – Networked Embedded Systems                     | Intro Design Project                    |

| 7    | 30.10.2019 | Lecture 5 – Networked Embedded Systems                     | Technical Support for Design Project    |

| 8    | 06.11.2019 | Lecture 6 – Networked Embedded Systems                     | Technical Support for Design Project    |

| 9    | 13.11.2019 | Lecture 7 - Networked Embedded Systems                     | Technical Support for Design Project    |

| 10   | 20.11.2019 | Lecture 8 - Modeling, Tools and Methods for Power Analysis | Technical Support for Design Project    |

| 11   | 27.11.2019 | Lecture 9 - Modeling, Tools and Methods for Power Analysis | Technical Support for Design Project    |

| 12   | 04.12.2019 | Lecture 10 - Renewable Energy                              | Technical Support for Design Project    |

| 13   | 11.12.2019 | Lecture 11 - Renewable Energy                              | Technical Support for Design Project    |

| 14   | 18.12.2019 | Lecture 12 - Project Presentations                         | Student Presentations of Design Project |

# **Daily Synopsis**

- Lecture (~60-75 min)

- Recap last lecture, introduce structure of topics & objective of today's lecture

- Daily lecture

- Feed in a daily

- Hot research topic/paper of the day

- Prominent research figure in the area

- Practical example (success story or failure)

- Recap objective of the day

- Reading and Writing Seminar (~30 min)

- Short presentation by group of students

- Discussion of papers

- Introduce reading for next week

- Exercises, Lab and Reading Time (2x 45 min)

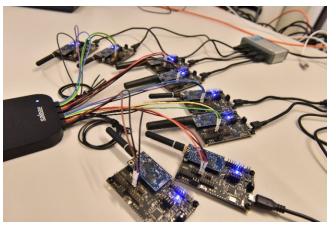

- Dual Processor Platform (DPP) on loan for everyone

- Introduction to DPP platform & FlockLab testbed

- DPP tutorial support

- Small design project in groups of 2-3 over whole length of the course

## Reading and Writing Seminar

- Reading assignment of 1 paper per week **until FRIDAY**

- 2-3 students prepare a written summary (max. 200-300 words)

- Write-up should contain the (i) essential points of the paper, (ii) it's main contribution and (iii) your assessment

- Research of related work: recent papers, different approaches, historical background...

- Summary is shared with all via discussion forum (matrix chatroom)

- Discussion/questions/comments FRIDAY to WEDNESDAY

- EVERYBODY comments on review summary and paper

- Your own opinion

- Corrections/additions to the reviewers voice

- Additional questions

- Joint search for related work, interesting ecosystem etc.

- Joint discussion of papers in class WEDNESDAY in class

- Short presentation of paper and summary in class to kick off discussion

- Presentation using max. 3-4 slides (not a full paper presentation)

- Reading/writing and your contributing to the discussions is part of the grade (30%)

- Assignment via signup sheet with

- 1x summary write-up/paper presentation

- 4x review/commenting per student

## Hands-on Practical Design Project

• Design project using Dual Processor Platform (DPP)

- In groups (of 2-3) develop a low-power application

- Introduction to state-of-the-art tools

- Effective power consumption effects should be visible

- Focus on aspects of dynamic range

- Presentation and discussion of results in final lecture

- Tournament: Best team is awarded a prize

### **Resources for Hands-on**

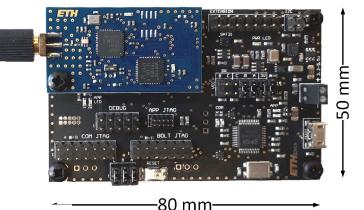

- Dual-Processor Platform

- State-of-the-Art Sensor network platform

- ETH-built...

STM32 CubeMX

DPP2 SX1262 ComBoard ST STM32L433CC, 256k ROM, 64k SRAM, 80 MHz RAM2 (16 KiB) has option for retention 0.28 µA (standby with RTC), 7 µs wakeup from stop mode –148 dB at (SF12, 125 kHz), 389 mW at +22 dB m LoRa, GFSK

### **Resources for Hands-on**

| Årm® Cartex®-M4(DSP + FPU)— 80 MHz |                                                                                 | STM32 L4<br>Product line                   | Flash<br>(KB)  | ram<br>(KB) | Memory<br>I/F<br>FSMC | Op-Amp | CAN | Sigma Delta<br>Interface | 12-bit ADC<br>5 Msps<br>16-bit HW<br>oversampling | DAC | SM | USB2.0 OTG FS | USB Device | Segment<br>LCD driver | Chrom-ART<br>Accelerator <sup>TM</sup> |

|------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------|----------------|-------------|-----------------------|--------|-----|--------------------------|---------------------------------------------------|-----|----|---------------|------------|-----------------------|----------------------------------------|

|                                    |                                                                                 | STM32L4x6 - USB OTG + Segment LCD Lines    |                |             |                       |        |     |                          |                                                   |     |    |               |            |                       |                                        |

|                                    |                                                                                 | STM32L496**                                | 512<br>to 1024 | 320         | •                     | 2      | 2   | 8x ch                    | 3                                                 | 2   | 2  | •             |            | Up to<br>8x40         | •                                      |

|                                    | ART Accelerator™     USART, SPI, I <sup>2</sup> C                               | STM32L476*                                 | 256<br>to 1024 | 128         | •                     | 2      | 1   | 8x ch                    | 3                                                 | 2   | 2  | •             |            | Up to<br>8x40         |                                        |

|                                    | Quad-SPI                                                                        | STM32L4x5 - USB 0TG lines                  |                |             |                       |        |     |                          |                                                   |     |    |               |            |                       |                                        |

|                                    | <ul> <li>16- and 32-bit timers</li> <li>SAI + audio PLL</li> </ul>              | STM32L475                                  | 256<br>to 1024 | 128         | •                     | 2      | 1   | 8x ch                    | 3                                                 | 2   | 2  | •             |            |                       |                                        |

|                                    | <ul> <li>SWP</li> <li>2x CAN</li> </ul>                                         | STM32L4x3 - USB Device + Segment LCD lines |                |             |                       |        |     |                          |                                                   |     |    |               |            |                       |                                        |

|                                    | 2x 12-bit DACs     Temperature sensor                                           | STM32L433*                                 | 128<br>to 256  | 64          |                       | 1      | 1   |                          | 1                                                 | 2   | 1  |               | •          | Up to<br>8x40         |                                        |

|                                    | Low voltage 1.71 to                                                             | STM32L4x2 - USB Device lines               |                |             |                       |        |     |                          |                                                   |     |    |               |            |                       |                                        |

|                                    | 3.6 V<br>• V <sub>ew</sub> mode<br>• Unique ID<br>• Capacitive touch<br>sensing | STM32L452*                                 | 256<br>to 512  | 160         |                       | 1      | 1   | 4x ch                    | 1                                                 | 1   | 1  |               | •          |                       |                                        |

|                                    |                                                                                 | STM32L432*                                 | 128<br>to 256  | 64          |                       | 1      | 1   |                          | 1                                                 | 2   | 1  |               | •          |                       |                                        |

|                                    | <ul> <li>AES-128/256*<br/>and SHA-256**</li> </ul>                              | STM32L412*                                 | 64<br>to 128   | 40          |                       | 1      |     |                          | 2                                                 |     |    |               | •          |                       |                                        |

|                                    |                                                                                 | STM32L4x1 - Access lines                   |                |             |                       |        |     |                          |                                                   |     |    |               |            |                       |                                        |

|                                    |                                                                                 | STM32L471                                  | 512<br>to 1024 | 128         | •                     | 2      | 1   | 8x ch                    | 3                                                 | 2   | 2  |               |            |                       |                                        |

|                                    |                                                                                 | STM32L451                                  | 256<br>to 512  | 160         |                       | 1      | 1   | 4x ch                    | 1                                                 | 1   | 1  |               |            |                       |                                        |

|                                    |                                                                                 | STM32L431                                  | 128<br>to 256  | 64          |                       | 1      | 1   |                          | 1                                                 | 2   | 1  |               |            |                       |                                        |

Note: \* HW crypto/hash functions are available on STM32L486, STM32L443, STM32L462, STM32L442 and STM32L422 - \*\* on STM32L4A6

## Resources for Hands-on

- DPP dev-board on loan for everyone for duration of semester

- FlockLab Testbed

- Testbed of 30+ nodes

- Remote programming of nodes

- Testing of applications in larger networks

- Power profiling, digital tracing/actuation

- FlockLab is a shared/limited resource

- Only one user active per time slice

- Need to accommodate everyone

- Cooja Simulator support

- Support through online forums and TA's

- Roman Trueb <u>roman.trueb@tik.ee.ethz.ch</u>

- Matthias Meyer <u>matthias.meyer@tik.ee.ethz.ch</u>

- Reto Da Forno <u>reto.daforno@tik.ee.ethz.ch</u>

http://www.flocklab.ethz.ch/

# Grading

- Official announcement

- 30% contributions to the reading/writing seminar

- 70% oral exam

- Hands-on design project

- A successful design project will count positive towards the oral exam grade

- Part of the oral exam will review your proposed solution and the concepts underlying the implementation

### Some Comments

- Course will mean quite some work for you.

- Reading takes some time. Use Wednesday afternoons.

- Will shift around timing as needed.

- Also we can discuss your topics/questions as needed.

- Hands-on design project was very successful in past years

- Depends on your own laptop infrastructure

- Need to share resources on FlockLab testbed

- Requires you to plan ahead (not just a last minute effort)

### LOW-POWER EMBEDDED SENSING SYSTEMS

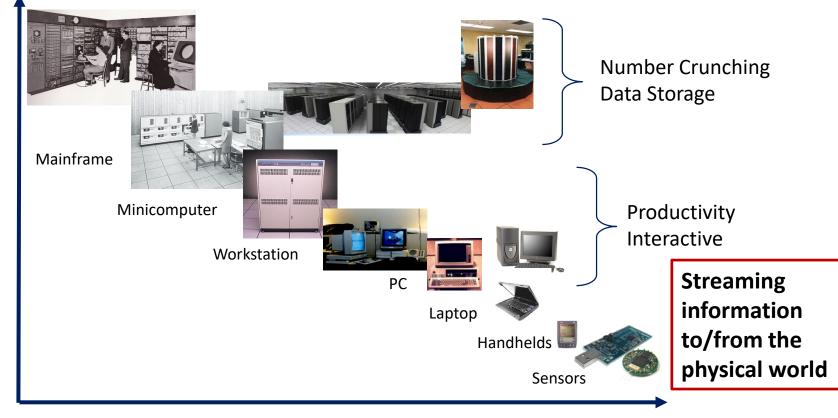

### **Bell's Law**: New class of Computers Emerges Every 10 Years

year

### Ever cheaper, ever smaller, ever more networked...

**ETH** zürich

Figure abridged from D. Culler

### The Network is the System

Power is an – issue at all system levels and scales

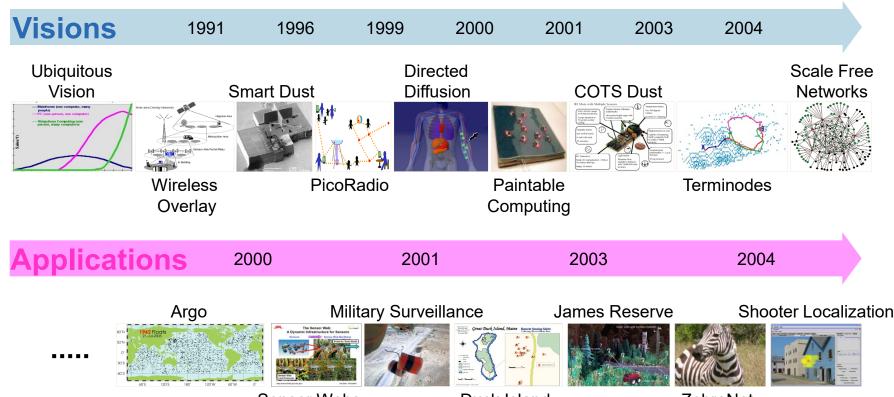

### Wireless Sensor Networks

Sensor Webs

Duck Island

ZebraNet

#### **E** *zürich*

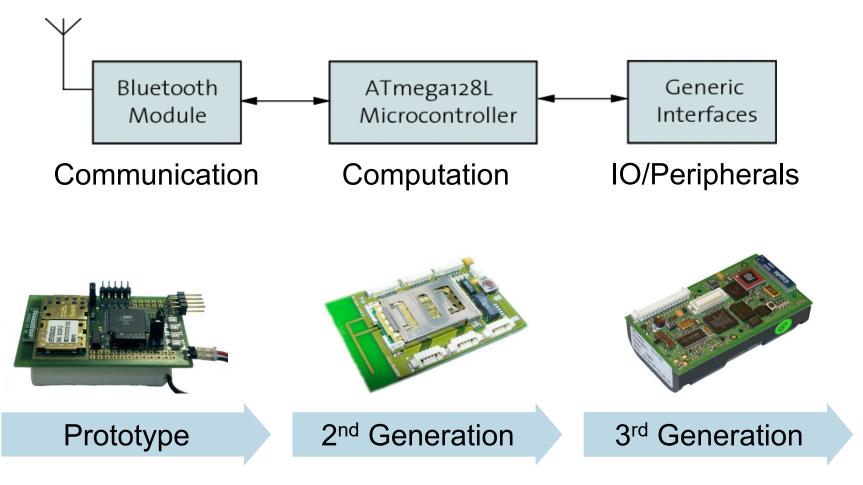

### **Typical Node Architecture**

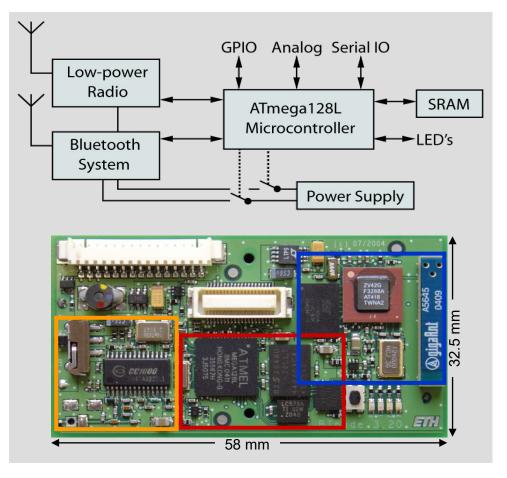

## BTnode rev3 Architecture Details

#### •System core

- Atmel ATmega128

- -256 kB SRAM

- Generic IO/Peripherals

- Switchable power supplies

### •Dual radio system

#### •Bluetooth radio

– 2.4 GHz Zeevo ZV4002

#### Low-power radio

- 433-915 MHz ISM Chipcon CC1000

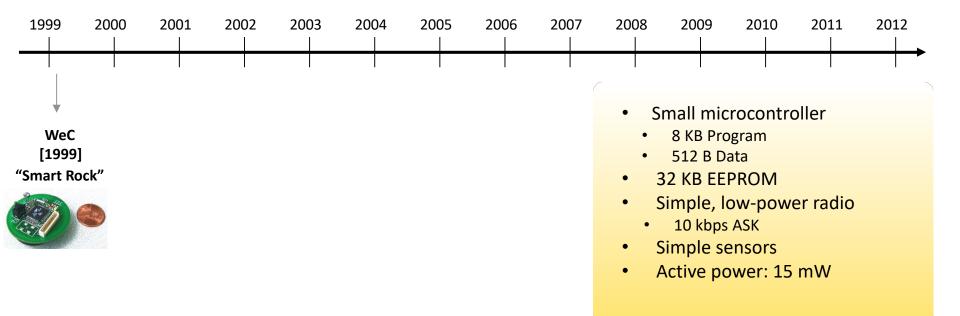

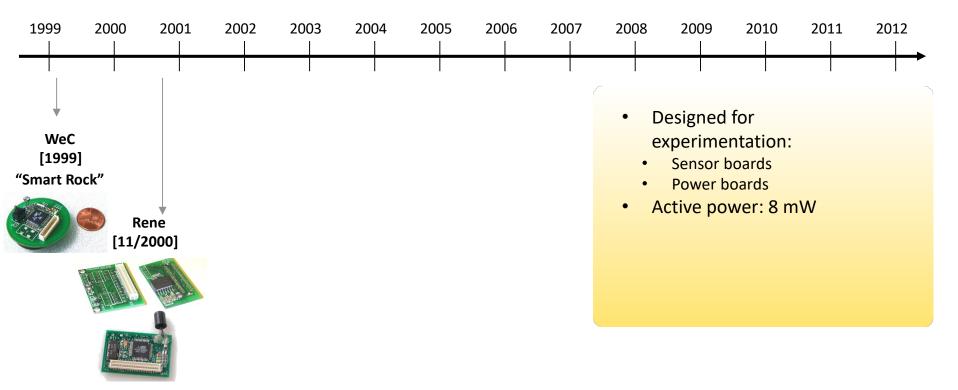

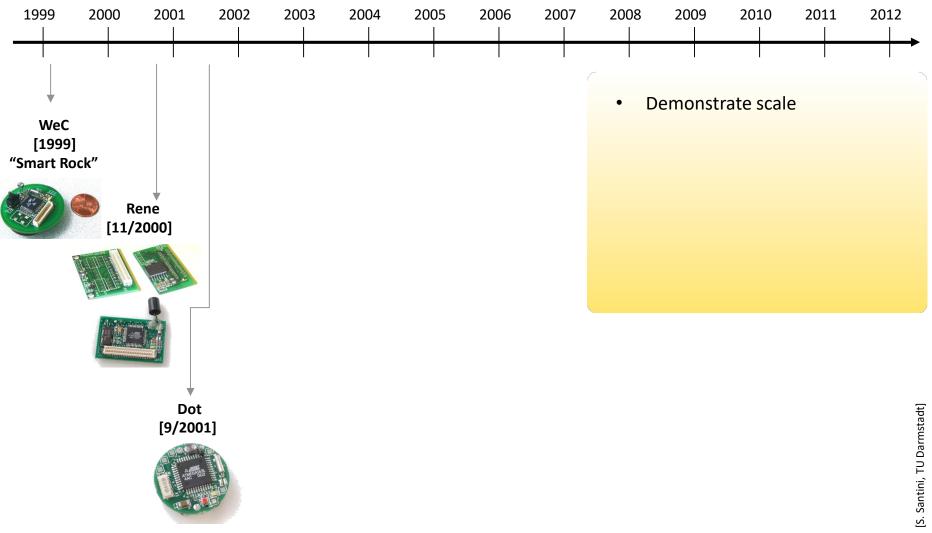

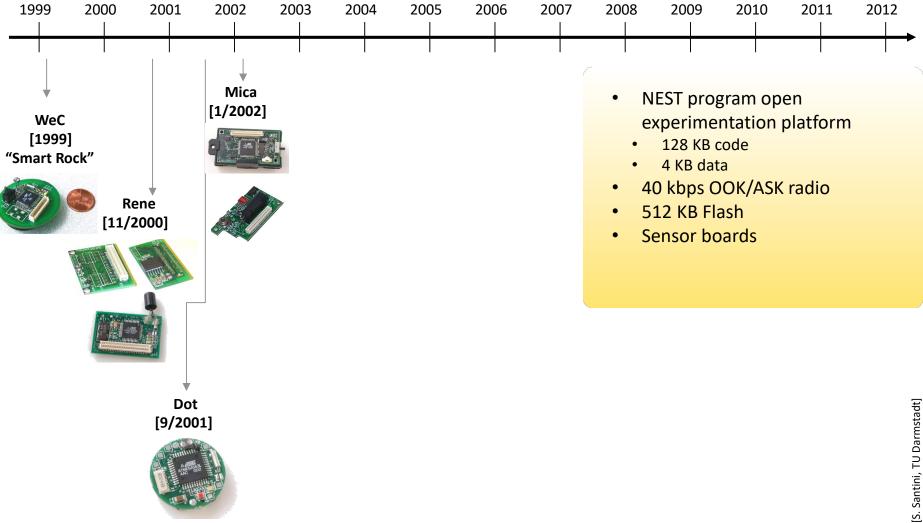

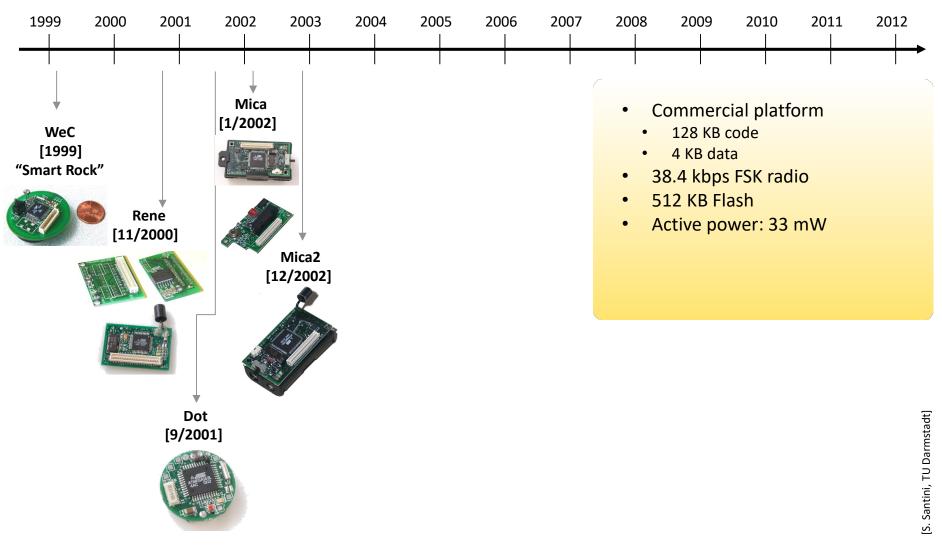

## **Basic Concepts of WSN Platforms**

- "Mote class" devices

- Microcontroller + low-power radio

- Battery powered

- Many custom applications

- Large design space, many variants

- Most prominent examples: Mica2, Mica2Dot, Tmote Sky

- Hardware is packaged with

- System software and apps

- Base stations, network access

- Server-side solutions (backends)

- Tools (e.g. simulators, virtual machines ...)

- First anticipation

- Small = cheap = low complexity = many is easy

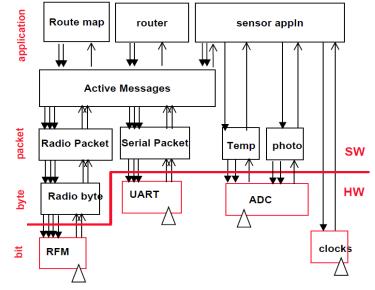

### A Popular Software System – TinyOS

- Event driven "Operating System"

- Written in nesC, a C dialect

- Geared towards simple applications (max. 10k RAM, 40 k ROM)

- Basically just a collection of drivers and an event queuing system

- Event handlers must not block...

- Compositional nature

- Hard- and software components

- Interfaces

- Modularity

- De-facto standard in WSN applications

- Popular in academia and industry

- Many (comparable) systems exist: Contiki, SOS, Mantis, BTnut...

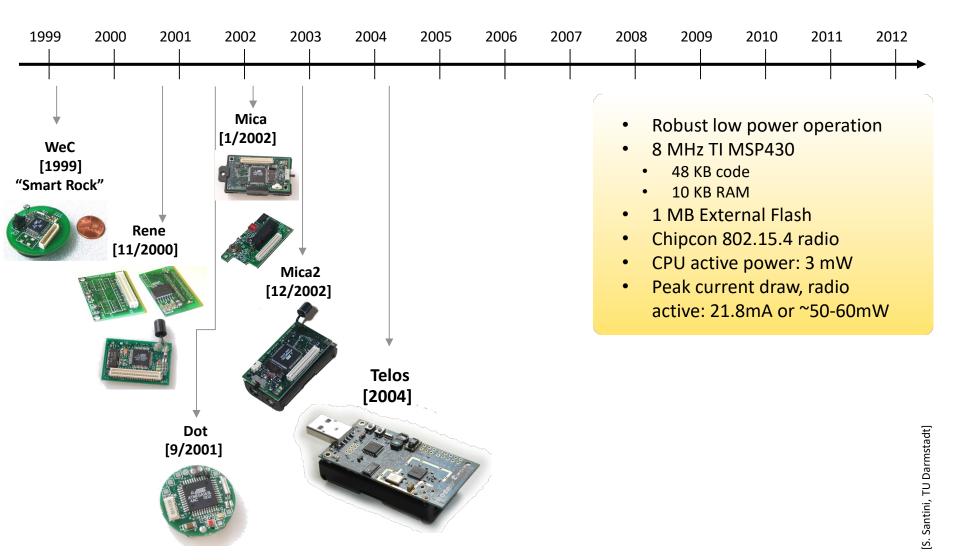

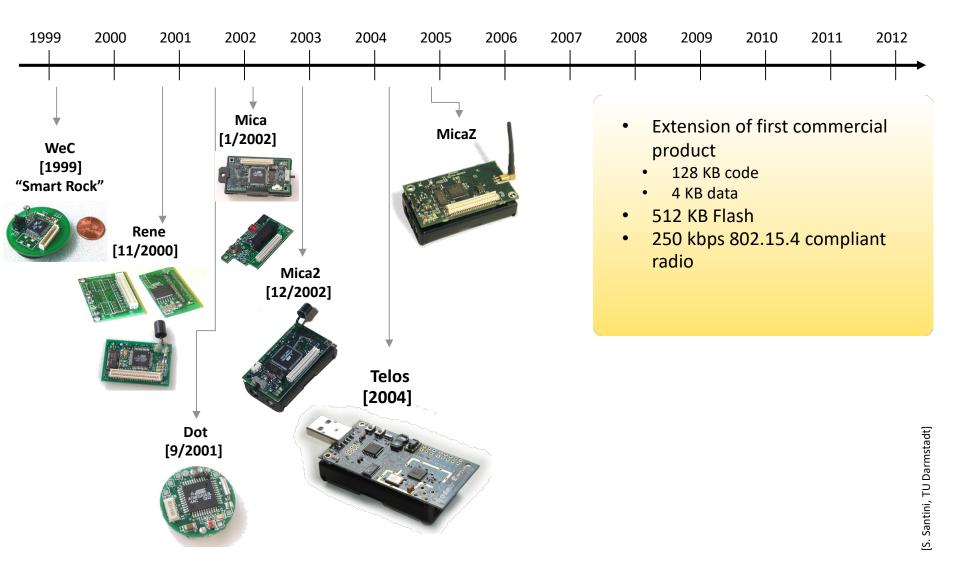

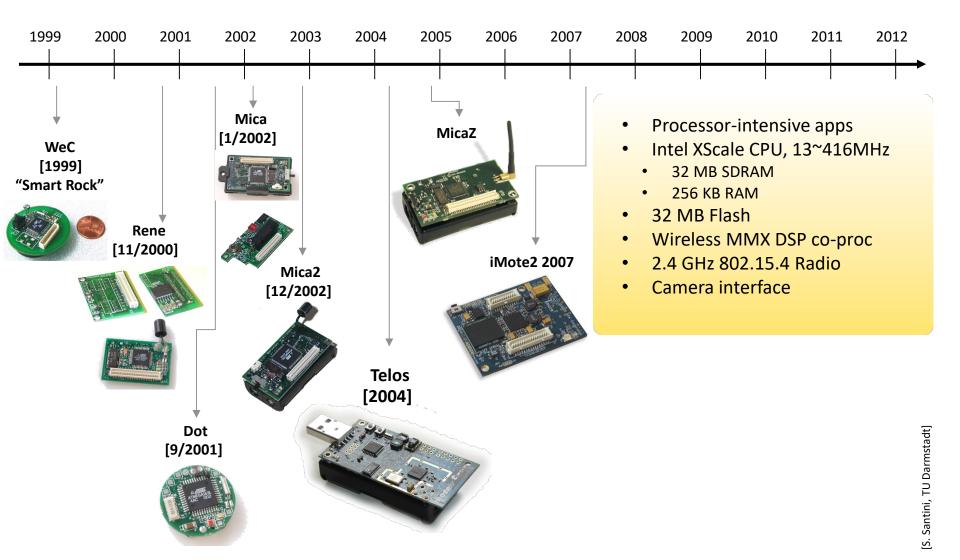

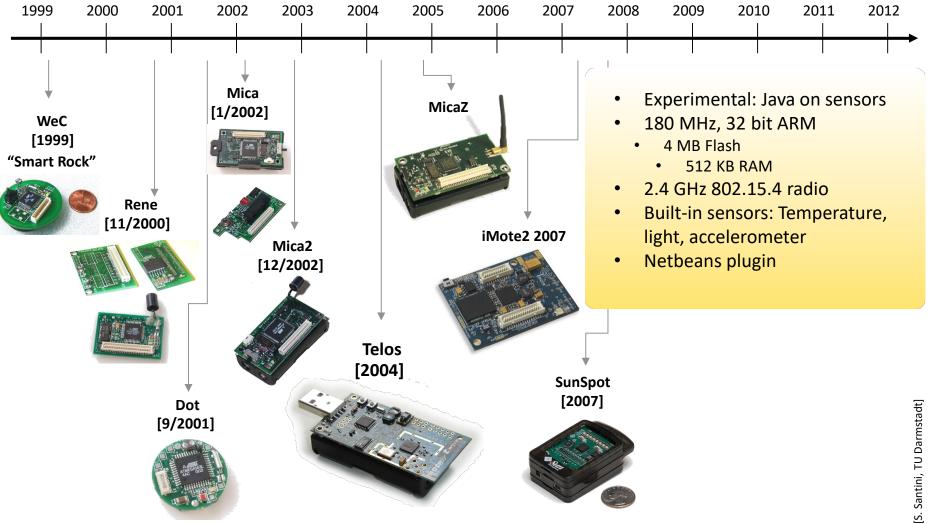

### **WSN Platform Variants**

### LOW-POWER SYSTEM ARCHITECTURES

Low-Power System Design

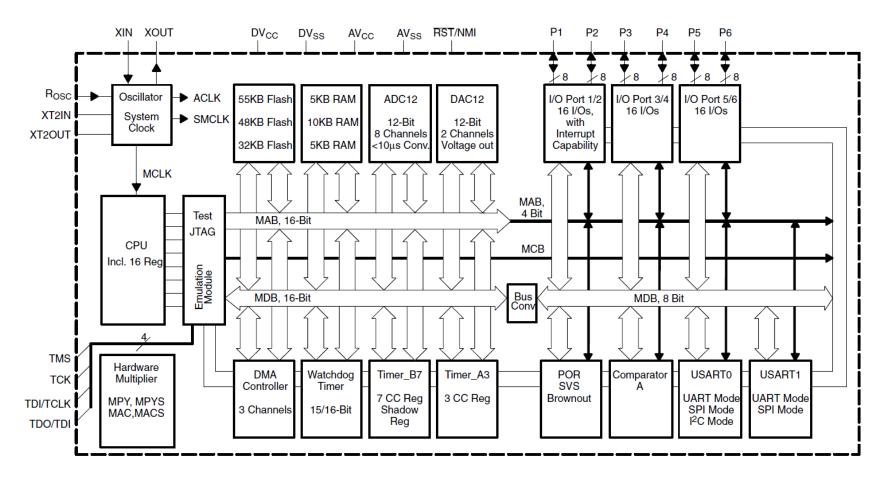

### MSP430x161x Specs

- Low Supply-Voltage Range, 1.8 V . . . 3.6 V

- Ultralow-Power Consumption:

- Active Mode: 330  $\mu\text{A}$  at 1 MHz, 2.2 V

- Standby Mode: 1.1 μA

- Off Mode (RAM Retention): 0.2 μA

- Five Power-Saving Modes

- Wake-Up From Standby Mode in less than 6 μs

- 16-Bit RISC Architecture, 125-ns Instruction Cycle Time

- Three-Channel Internal DMA

- 12-Bit A/D Converter With Internal Reference, Sample-and-Hold and Autoscan Feature

- Dual 12-Bit D/A Converters With Synchronization

- 16-Bit Timer\_A With Three Capture/Compare Registers

- 16-Bit Timer\_B With Three or Seven Capture/Compare-With-Shadow Registers

- On-Chip Comparator

- Serial Communication Interface (USART0), Functions as Asynchronous UART or Synchronous SPI or I<sup>2</sup>C<sup>TM</sup> Interface

- Serial Communication Interface (USART1), Functions as Asynchronous UART or Synchronous SPI Interface

- Supply Voltage Supervisor/Monitor With Programmable Level Detection

- Serial Onboard Programming, No External Programming Voltage Needed Programmable Code Protection by Security Fuse

- Family Members Include:

- MSP430F155: 16KB+256B Flash Memory 512B RAM

- MSP430F156: 24KB+256B Flash Memory

- 1KB RAM

- MSP430F157: 32KB+256B Flash Memory, 1KB RAM

- MSP430F167: 32KB+256B Flash Memory, 1KB RAM

- MSP430F168: 48KB+256B Flash Memory, 2KB RAM

### MSP430x161x Internals

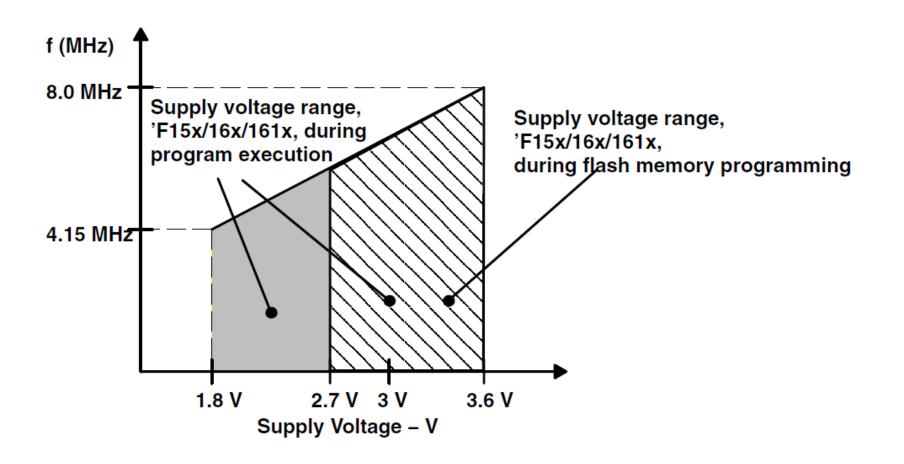

### Frequency vs. Supply Voltage Max Range

### **Estimating Frequency and Voltage Effects**

- Dynamic power (switching power) dissipated per unit of time  $P = C \cdot V^2 \cdot A \cdot f$

- Current consumption of active mode versus system frequency  $I_{(AM)} = I_{(AM)} [1 \text{ MHz}] \times f(\text{System}) [\text{MHz}]$

- Current consumption of active mode versus supply voltage  $I_{(AM)} = I_{(AM)} [3 V] + 210 \mu A/V \times (VCC - 3 V)$

- Example:

-

$$f_{(SMCLK)}$$

= 1 MHz; Vcc = 2.2V => Nominal I<sub>(AM)</sub>=330 uA

### LP Mode Standard Operating Conditions

MSP430F161x supply current into  $AV_{CC} + DV_{CC}$  excluding external current ( $AV_{CC} = DV_{CC} = V_{CC}$ )

|                     | PARAMETER                                                                                                                                                    | TEST COND                             | ITIONS                                           | MIN | NOM        | MAX              | UNIT       |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------------------------------------------|-----|------------|------------------|------------|

|                     | Active mode, (see Note 1)<br>$f_{(MCLK)} = f_{(SMCLK)} = 1 \text{ MHz},$<br>$f_{(ACLK)} = 32,768 \text{ Hz}$<br>XTS=0,  SELM=(0,1)                           | $T_A = -40^{\circ}C$ to $85^{\circ}C$ | V <sub>CC</sub> = 2.2 V<br>V <sub>CC</sub> = 3 V |     | 330<br>500 | 400<br>600       | μ <b>A</b> |

| l <sub>(AM)</sub>   | Active mode, (see Note 1)<br>f(MCLK) = f(SMCLK) = 4,096 Hz,                                                                                                  | T <sub>A</sub> = −40°C to 85°C        | V <sub>CC</sub> = 2.2 V                          |     | 2.5        | 7                | μA         |

|                     | f <sub>(ACLK)</sub> = 4,096 Hz<br>XTS=0, SELM=3                                                                                                              |                                       | $V_{CC} = 3 V$                                   |     | 9          | 20               | μΛ         |

| I <sub>(LPM0)</sub> | Low-power mode, (LPM0)<br>f <sub>(MCLK)</sub> = 0 MHz, f <sub>(SMCLK)</sub> = 1 MHz,<br>f <sub>(ACLK)</sub> = 32,768 Hz<br>XTS=0, SELM=(0,1)<br>(see Note 1) | T <sub>A</sub> = −40°C to 85°C        | V <sub>CC</sub> = 2.2 V                          |     | 50         | 60               | μA         |

|                     |                                                                                                                                                              | TA = -40 0 10 00 0                    | V <sub>CC</sub> = 3 V                            |     | 75         | 95               | μΑ         |

|                     | Low-power mode, (LPM2),                                                                                                                                      |                                       | $V_{CC} = 2.2 V$                                 |     | 11         | 14               |            |

| I <sub>(LPM2)</sub> |                                                                                                                                                              | $T_A = -40^{\circ}C$ to $85^{\circ}C$ | V <sub>CC</sub> = 3 V                            |     | 17         | 22               | μA         |

|                     |                                                                                                                                                              | $T_A = -40^{\circ}C$                  |                                                  |     | 1.3        | 1.6              | μΑ         |

|                     | Low-power mode, (LPM3)<br>$f_{(MCLK)} = f_{(SMCLK)} = 0$ MHz,<br>$f_{(ACLK)} = 32,768$ Hz, SCG0 = 1<br>(see Note 2)                                          | $T_A = 25^{\circ}C$                   | V <sub>CC</sub> = 2.2 V                          |     | 1.3        | 1.6              |            |

| 1                   |                                                                                                                                                              | $T_A = 85^{\circ}C$                   |                                                  |     | 3.0        | 6.0              |            |

| I <sub>(LPM3)</sub> |                                                                                                                                                              | $T_A = -40^{\circ}C$                  |                                                  |     | 2.6        | 3.0              |            |

|                     |                                                                                                                                                              | $T_A = 25^{\circ}C$                   | V <sub>CC</sub> = 3 V                            |     | 2.6        | 3.0              |            |

|                     |                                                                                                                                                              | $T_A = 85^{\circ}C$                   |                                                  |     | 4.4        | 8.0              |            |

|                     | Low-power mode, (LPM4)                                                                                                                                       | $T_A = -40^{\circ}C$                  |                                                  |     | 0.2        | 0.5              | μΑ         |

| l <sub>(LPM4)</sub> | $f_{(MCLK)} = 0 \text{ MHz}, f_{(SMCLK)} = 0 \text{ MHz},$                                                                                                   | $T_A = 25^{\circ}C$                   | V <sub>CC</sub> =<br>2.2V / 3 V                  |     | 0.2        | 0.5              |            |

| · ·                 | $f_{(ACLK)} = 0$ Hz, SCG0 = 1                                                                                                                                | $T_A = 85^{\circ}C$                   |                                                  |     | 2.0        | <mark>5.0</mark> |            |

NOTES: 1. Timer\_B is clocked by f(DCOCLK) = 1 MHz. All inputs are tied to 0 V or to V<sub>CC</sub>. Outputs do not source or sink any current.

WDT is clocked by f<sub>(ACLK)</sub> = 32,768 Hz. All inputs are tied to 0 V or to V<sub>CC</sub>. Outputs do not source or sink any current. The current consumption in LPM2 and LPM3 are measured with ACLK selected.

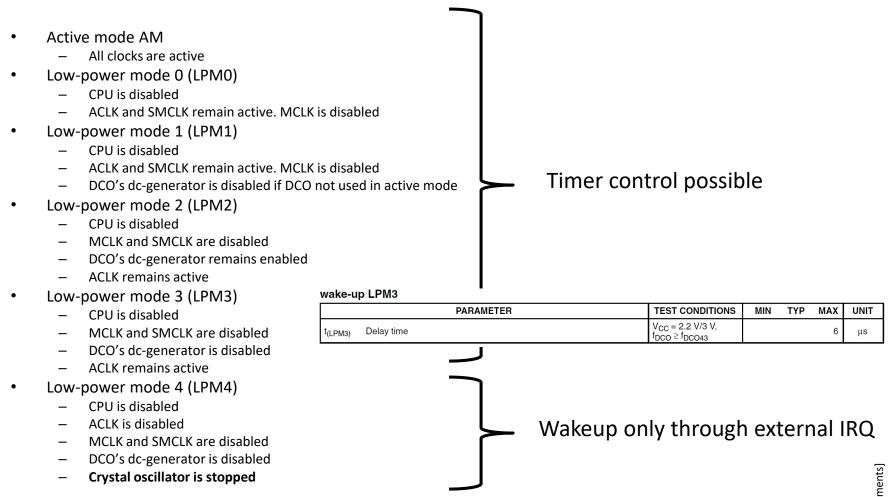

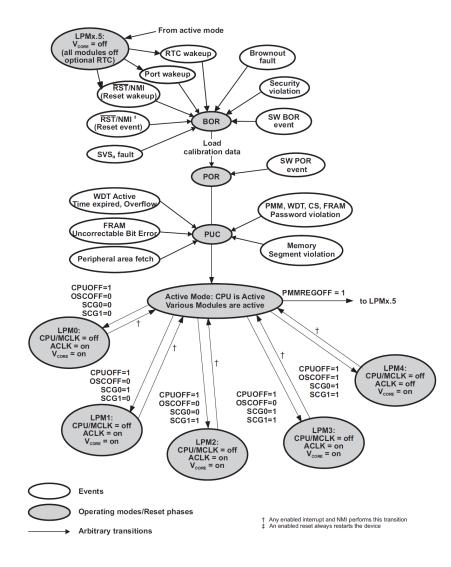

# MSP430x161x Low Power Modes

[Texas Instruments]

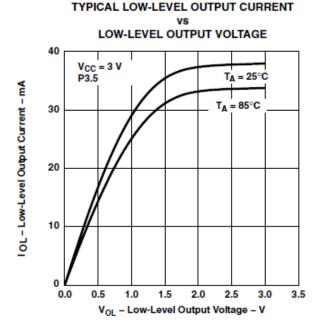

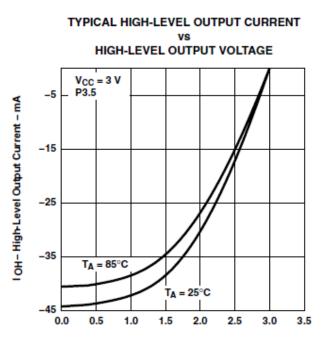

## What is External Current?

#### leakage current - Ports P1, P2, P3, P4, P5 and P6 (see Note 1)

| PARAMETER              |                    |         | TEST CONDITION                   | S MIN TYP                   |  |  | MAX | UNIT |

|------------------------|--------------------|---------|----------------------------------|-----------------------------|--|--|-----|------|

| I <sub>lkg(Px.y)</sub> | Leakage<br>current | Port Px | V <sub>(Px.y)</sub> (see Note 2) | V <sub>CC</sub> = 2.2 V/3 V |  |  | ±50 | nA   |

NOTES: 1. The leakage current is measured with V<sub>SS</sub> or V<sub>CC</sub> applied to the corresponding pin(s), unless otherwise noted.

2. The port pin must be selected as input.

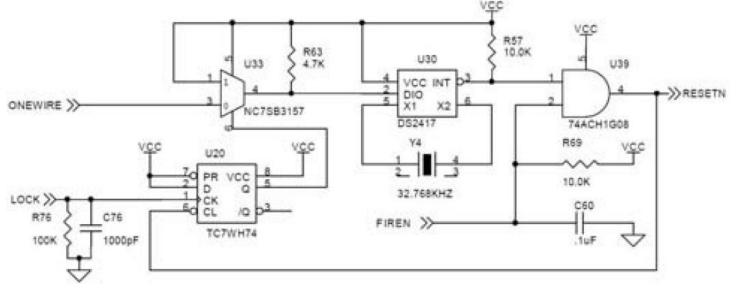

### External Wakeup: XSM Grenade Timer

- External clock circuit triggering IRQ-based wakeup

- DS2417 I<sub>cc</sub>=2 uA

- D-FlipFlop  $I_{cc}$ =2.0 uA @ 25°C, max. 20uA @ -40-85°C

- Other logic...

- Today this is integrated in modern SOCs

Dutta, P., Grimmer, M., Arora, A., Bibykt, S., & Culler, D. (2005). Design of a wireless sensor network platform for detecting rare, random, and ephemeral events. IPSN 2005 (Vol. 2005, pp. 497–502).

# MSP Family Variant: MSP430x241x

- Low Supply-Voltage Range, 1.8 V to 3.6 V

- Ultralow-Power Consumption:

- Active Mode: 365 µA at 1 MHz, 2.2 V

- Standby Mode (VLO): 0.5 μA

- Off Mode (RAM Retention): 0.1 μA

- Wake-Up From Standby Mode in Less Than 1 μs

- 16-Bit RISC Architecture, 62.5-nsInstruction Cycle Time

- Three-Channel Internal DMA

- 12-Bit Analog-to-Digital (A/D) Converter With Internal Reference, Sample-and-Hold, and Autoscan Feature

- Dual 12-Bit Digital-to-Analog (D/A) Converters With Synchronization

- 16-Bit Timer\_A With Three Capture/Compare Registers

- 16-Bit Timer\_B With Seven Capture/Compare-With-Shadow Registers

- On-Chip Comparator

- Four Universal Serial Communication Interfaces (USCIs)

- USCI\_A0 and USCI\_A1

- Enhanced UART Supporting Auto-Baudrate Detection

- IrDA Encoder and Decoder

- Synchronous SPI

- USCI\_B0 and USCI\_B1

- I<sup>2</sup>C<sup>™</sup>

- Synchronous SPI

- Supply Voltage Supervisor/Monitor With Programmable Level Detection

- Brownout Detector

- Bootstrap Loader

- Serial Onboard Programming, No External Programming Voltage Needed Programmable Code Protection by Security Fuse

- Family Members Include:

- MSP430F2416:

92KB+256B Flash Memory, 4KB RAM

- MSP430F2417:

92KB+256B Flash Memory, 8KB RAM

- MSP430F2418: 116KB+256B Flash Memory, 8KB RAM

- MSP430F2419: 120KB+256B Flash Memory, 4KB RAM

- MSP430F2616: 92KB+256B Flash Memory, 4KB RAM

- MSP430F2617: 92KB+256B Flash Memory, 8KB RAM

- MSP430F2618: 116KB+256B Flash Memory, 8KB RAM

- MSP430F2619: 120KB+256B Flash Memory, 4KB RAM

- Available in 80-Pin Quad Flat Pack (QFP) and 64-Pin QFP (See Available Options)

- For Complete Module Descriptions, See the MSP430x2xx Family User's Guide, Literature Number SLAU144

- <sup>†</sup> The MSP430F241x devices are identical to the MSP430F261x devices, with the exception that the DAC12 modules and the DMA controller are not implemented.

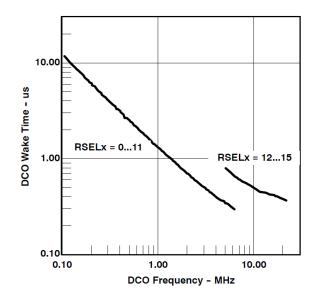

# What Really Changed?

#### wake-up from low-power modes (LPM3/LPM4)

|                         | PARAMETER                                    | TEST CONDITIONS                                 | VCC       | MIN TYP                                           | MAX | UNIT |

|-------------------------|----------------------------------------------|-------------------------------------------------|-----------|---------------------------------------------------|-----|------|

| t <sub>DCO,LPM3/4</sub> |                                              | BCSCTL1= CALBC1_1MHz,<br>DCOCTL = CALDCO_1MHz   | 2.2 V/3 V |                                                   | 2   |      |

|                         | DCO clock wake-up time from LPM3/4           | BCSCTL1= CALBC1_8MHz,<br>DCOCTL = CALDCO_8MHz   | 2.2 V/3 V |                                                   |     |      |

|                         | (see Note 1)                                 | BCSCTL1= CALBC1_12MHz,<br>DCOCTL = CALDCO_12MHz | - 22//3/  |                                                   | 1   | μs   |

|                         |                                              | BCSCTL1= CALBC1_16MHz,<br>DCOCTL = CALDCO_16MHz | 3 V       | 1                                                 |     |      |

| t <sub>CPU,LPM3/4</sub> | CPU wake-up time from LPM3/4<br>(see Note 2) |                                                 |           | 1/f <sub>MCLK</sub> +<br>t <sub>Clock,LPM3/</sub> | 4   |      |

NOTES: 1. The DCO clock wake-up time is measured from the edge of an external wake-up signal (e.g., port interrupt) to the first clock edge observable externally on a clock pin (MCLK or SMCLK).

2. Parameter applicable only if DCOCLK is used for MCLK.

# MSP430x161x Memory Subsystem

#### **Flash Memory**

|                                 | PARAMETER                                           | TEST<br>CONDITIONS  | V <sub>cc</sub> | MIN NOM MAX     |                 |     | UNIT             |

|---------------------------------|-----------------------------------------------------|---------------------|-----------------|-----------------|-----------------|-----|------------------|

| V <sub>CC(PGM</sub> /<br>ERASE) | Program and Erase supply voltage                    |                     |                 | 2.7             |                 | 3.6 | V                |

| f <sub>FTG</sub>                | Flash Timing Generator frequency                    |                     |                 | 257             |                 | 476 | kHz              |

| I <sub>PGM</sub>                | Supply current from DV <sub>CC</sub> during program |                     | 2.7 V/ 3.6 V    |                 | 3               | 5   | mA               |

| I <sub>ERASE</sub>              | Supply current from DV <sub>CC</sub> during erase   |                     | 2.7 V/ 3.6 V    |                 | 3               | 7   | mA               |

| t <sub>CPT</sub>                | Cumulative program time                             | see Note 1          | 2.7 V/ 3.6 V    |                 |                 | 4   | ms               |

| t <sub>CMErase</sub>            | Cumulative mass erase time                          | see Note 2          | 2.7 V/ 3.6 V    | 200             |                 |     | ms               |

|                                 | Program/Erase endurance                             |                     |                 | 10 <sup>4</sup> | 10 <sup>5</sup> |     | cycles           |

| t <sub>Retention</sub>          | Data retention duration                             | $T_J = 25^{\circ}C$ |                 | 100             |                 |     | years            |

| t <sub>Word</sub>               | Word or byte program time                           |                     |                 |                 | 35              |     |                  |

| t <sub>Block, 0</sub>           | Block program time for 1 <sup>st</sup> byte or word |                     |                 |                 | 30              |     |                  |

| t <sub>Block, 1-63</sub>        | Block program time for each additional byte or word |                     |                 |                 | 21              |     |                  |

| t <sub>Block, End</sub>         | Block program end-sequence wait time                | see Note 3          |                 |                 | 6               |     | t <sub>FTG</sub> |

| t <sub>Mass Erase</sub>         | Mass erase time                                     | ]                   |                 | 5297            |                 |     |                  |

| t <sub>Seg Erase</sub>          | Segment erase time                                  |                     |                 |                 | 4819            |     |                  |

NOTES: 1. The cumulative program time must not be exceeded when writing to a 64-byte flash block. This parameter applies to all programming methods: individual word/byte write and block write modes.

The mass erase duration generated by the flash timing generator is at least 11.1ms (= 5297x1/f<sub>FTG</sub>,max = 5297x1/476kHz). To achieve the required cumulative mass erase time the Flash Controller's mass erase operation can be repeated until this time is met. (A worst case minimum of 19 cycles are required).

3. These values are hardwired into the Flash Controller's state machine ( $t_{FTG} = 1/f_{FTG}$ ).

### MSP Family Variant: MSP430FR59xx

- Embedded Microcontroller

- 16-Bit RISC Architecture up to 16-MHz Clock

- Wide Supply Voltage Range (1.8 V <sup>(1)</sup> to 3.6 V)

- Optimized Ultralow-Power Modes

| Mode                                  | Consumption<br>(Typical) |

|---------------------------------------|--------------------------|

| Active Mode                           | 103 µA/MHz               |

| Standby (LPM3 With VLO)               | 0.4 µA                   |

| Real-Time Clock (LPM3.5 With Crystal) | 0.5 µA                   |

| Shutdown (LPM4.5)                     | 0.02 µA                  |

- Ultralow-Power Ferroelectric RAM (FRAM)

- Up to 64KB Nonvolatile Memory

- Ultralow-Power Writes

- Fast Write at 125 ns Per Word (64KB in 4 ms)

- Unified Memory = Program + Data + Storage in One Single Space

- 10<sup>15</sup> Write Cycle Endurance

- Radiation Resistant and Nonmagnetic

- Intelligent Digital Peripherals

- 32-Bit Hardware Multiplier (MPY)

- Three-Channel Internal DMA

- Real-Time Clock (RTC) With Calendar and Alarm Functions

- Five 16-Bit Timers With up to Seven Capture/Compare Registers Each

- 16-Bit Cyclic Redundancy Checker (CRC)

- High-Performance Analog

- 16-Channel Analog Comparator

- 14-Channel 12-Bit Analog-to-Digital Converter (ADC) With Internal Reference and Sample-and-Hold

- 200 ksps at 75-µA Consumption

- Multifunction Input/Output Ports

- All Pins Support Capacitive Touch Capability With No Need for External Components

- Accessible Bit-, Byte-, and Word-Wise (in Pairs)

- Edge-Selectable Wake From LPM on All Ports

- Programmable Pullup and Pulldown on All Ports

- Code Security and Encryption

- 128-Bit or 256-Bit AES Security Encryption and Decryption Coprocessor (MSP430FR59xx Only)

- Random Number Seed for Random Number Generation Algorithms

- Enhanced Serial Communication

- eUSCI\_A0 and eUSCI\_A1 Support

- UART With Automatic Baud-Rate Detection

- IrDA Encode and Decode

- SPI at Rates up to 10 Mbps

- eUSCI\_B0 Supports

- I<sup>2</sup>C With Multiple Slave Addressing

- SPI at Rates up to 8 Mbps

- Hardware UART and I<sup>2</sup>C Bootstrap Loader (BSL)

- Flexible Clock System

- Fixed-Frequency DCO With 10 Selectable Factory-Trimmed Frequencies

- Low-Power Low-Frequency Internal Clock Source (VLO)

- 32-kHz Crystals (LFXT)

- High-Frequency Crystals (HFXT)

- Development Tools and Software

- Professional Development Environments

- Development Kit (MSP-TS430RGZ48C)

- Family Members

- Table 2 Summarizes 18 Variants in 3 Available Package Types

- For Complete Module Descriptions, See the MSP430FR59xx and MSP430FR58xx Family User's Guide (SLAU367)

### MSP430FRxx Storage Alternative: FRAM

- Ferroelectric RAM (FRAM)

- Random-access memory similar in construction to DRAM

- Uses a ferroelectric layer instead of a dielectric layer to achieve nonvolatility

- Growing number of alternative non-volatile random-access memory offering the same functionality as flash memory

- Lower power usage

- Faster write performance

- Greater maximum number of write-erase cycles (>10<sup>16</sup>)

- Lower storage densities

- Storage capacity limitations

- Higher cost

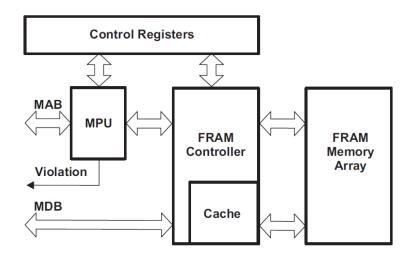

### **FRAM Necessitates a Dedicated Controller**

- Byte or word write access

- Automatic and programmable wait state control

- Error correction code (bit errors)

- Cache for fast reads

- Power control when not using FRAM

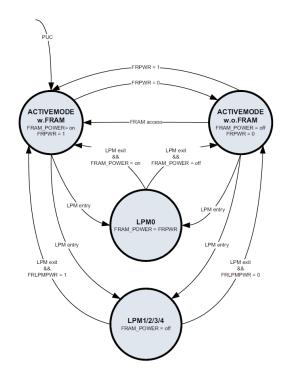

### MSP430FR5969 Low Power Modes

| Mode                                     | Active | LPMO  | LPM1  | LPM2              | LPM3              | LPM4        | LPM4.5                  |

|------------------------------------------|--------|-------|-------|-------------------|-------------------|-------------|-------------------------|

| Current @ 1<br>MHz [μA]                  | 128    | 86    | 47    |                   |                   |             |                         |

| Current @ 8<br>MHz [µA]                  | 470    | 151   | 112   | 0.81              | 0.56              | 0.48        | 0.04                    |

| Current @ 16<br>MHz [µA]                 | 855    | 213   | 174   |                   |                   |             |                         |

| Wake-up<br>delay [µs]                    | -      | 0.25  | 5.75  | 6                 | 6                 | 6           | <b>875</b> <sup>2</sup> |

| CPU / FRAM                               | 1      | 0     | 0     | 0                 | 0                 | 0           | 0                       |

| HF / LF / UC<br>Peripherals <sup>1</sup> | 1/1/1  | 1/1/1 | 1/1/1 | 0/1/1             | 0/1/1             | 0/0/1       | 0/0/0                   |

| Full retention                           | 1      | 1     | 1     | 1                 | 1                 | 1           | 0                       |

| Wake-up<br>events                        | -      | all   | all   | I/O<br>comp<br>LF | I/O<br>comp<br>LF | I/O<br>comp | I/O                     |

<sup>1</sup> HF = high frequency (SMCLK), LF = low frequency (ACLK), UC = unclocked (external clock)

<sup>2</sup> not included is the time needed to reinitialize the MCU after the reset

### State Transitions: It Looks Straightforward...

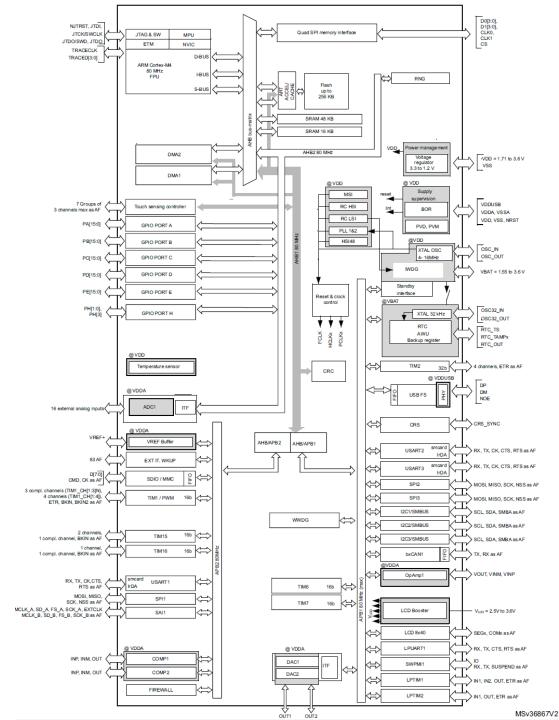

# STM32L433xx

#### Ultra-low-power Arm<sup>®</sup> Cortex<sup>®</sup>-M4 32-bit MCU+FPU, 100DMIPS, up to 256KB Flash, 64KB SRAM, USB FS, LCD, ext. SMPS

Datasheet - production data

STM32L433xx

#### Features

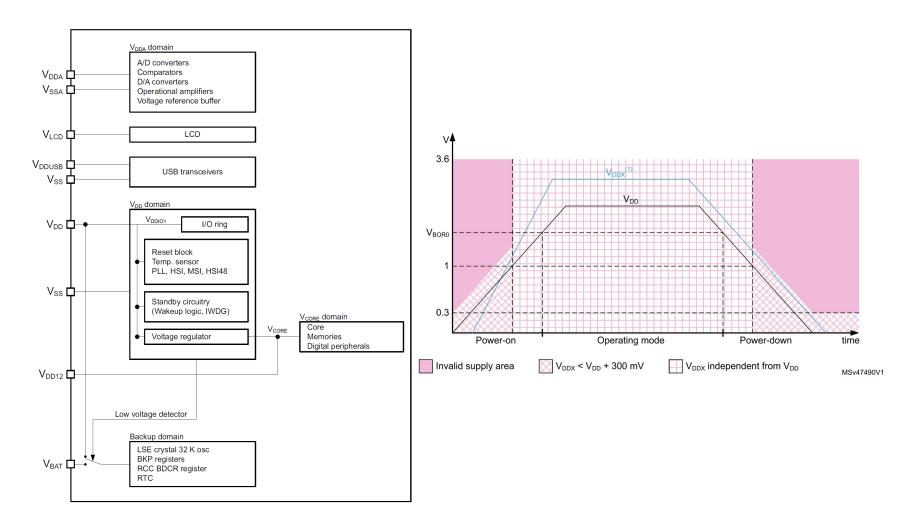

- Ultra-low-power with FlexPowerControl

- 1.71 V to 3.6 V power supply

- -40 °C to 85/105/125 °C temperature range

- 200 nA in V<sub>BAT</sub> mode: supply for RTC and 32x32-bit backup registers

- 8 nA Shutdown mode (5 wakeup pins)

- 28 nA Standby mode (5 wakeup pins)

- 280 nA Standby mode with RTC \_

- 1.0 µA Stop 2 mode, 1.28 µA with RTC

- 84 µA/MHz run mode (LDO Mode)

- 36 µA/MHz run mode (@3.3 V SMPS Mode)

- Batch acquisition mode (BAM) -

- 4 us wakeup from Stop mode

- Brown out reset (BOR) \_

- Interconnect matrix

- Core: Arm<sup>®</sup> 32-bit Cortex<sup>®</sup>-M4 CPU with FPU Adaptive real-time accelerator (ART Accelerator™) allowing 0-wait-state execution from Flash memory, frequency up to 80 MHz, MPU, 100DMIPS and DSP instructions

- Performance benchmark

- 1.25 DMIPS/MHz (Drystone 2.1)

- 273.55 CoreMark<sup>®</sup> (3.42 CoreMark/MHz @ 80 MHz)

- Energy benchmark

- 253 ULPBench<sup>®</sup> score

- Clock Sources

- 4 to 48 MHz crystal oscillator

- 32 kHz crystal oscillator for RTC (LSE)

- Internal 16 MHz factory-trimmed RC (±1%) \_

- Internal low-power 32 kHz RC (±5%) \_

- Internal multispeed 100 kHz to 48 MHz oscillator, auto-trimmed by LSE (better than ±0.25 % accuracy)

- Internal 48 MHz with clock recovery

- 2 PLLs for system clock, USB, audio, ADC

- UFBGA64 (5x5) WLCSP49

- Up to 83 fast I/Os, most 5 V-tolerant

- · RTC with HW calendar, alarms and calibration

- LCD 8× 40 or 4× 44 with step-up converter

- Up to 21 capacitive sensing channels: support touchkey, linear and rotary touch sensors

- 11x timers: 1x 16-bit advanced motor-control, 1x 32-bit and 2x 16-bit general purpose, 2x 16bit basic, 2x low-power 16-bit timers (available in Stop mode), 2x watchdogs, SysTick timer

- Memories

- Up to 256 KB single bank Flash, proprietary code readout protection

- 64 KB of SRAM including 16 KB with hardware parity check

- Quad SPI memory interface

- Rich analog peripherals (independent supply)

- 1x 12-bit ADC 5 Msps, up to 16-bit with hardware oversampling, 200 µA/Msps

- 2x 12-bit DAC output channels, low-power sample and hold

- 1x operational amplifier with built-in PGA

- 2x ultra-low-power comparators

- 17x communication interfaces

- USB 2.0 full-speed crystal less solution with LPM and BCD

- 1x SAI (serial audio interface)

- 3x I2C FM+(1 Mbit/s), SMBus/PMBus

- 4x USARTs (ISO 7816, LIN, IrDA, modem)

- 1x LPUART (Stop 2 wake-up)

- 3x SPIs (and 1x Quad SPI)

- CAN (2.0B Active) and SDMMC interface

- SWPMI single wire protocol master I/F

- IRTIM (Infrared interface)

DS11449 Rev 5

[ST Microelectronics]

# STM32L433xx

### STM32L433xx

## Principles for Low-Power Applications

- Reduce power consumption by maximizing time in low-power modes (LPM3 or LPM4)

- Interrupts to wake the processor and control program flow

- Peripherals should be switched on only when needed

- Low-power integrated peripheral modules in place of SW functions

- Timer\_A and Timer\_B automatically captures external timing or PWM

- Direct Memory Access (DMA)

- Calculated branching and fast table look-ups should be used in place of flag polling and long software calculations

- Avoid frequent subroutine and function calls due to overhead

- For longer software routines, single-cycle CPU registers should be used

- For low duty cycles and slow response time events, maximizing time in LPMx.5 can further reduce power

## WIRELESS SENSOR NETWORK APPLICATION EXAMPLE

Low-Power System Design

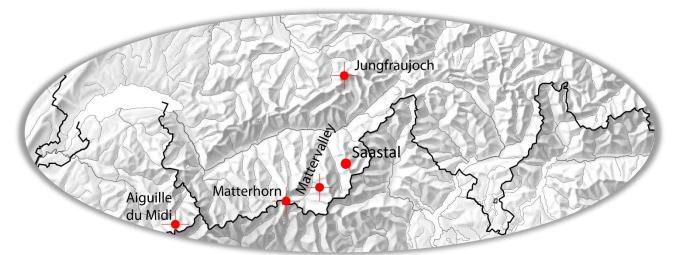

### PermaSense

- Interdisciplinary geo-science and engineering collaboration

- Consortium of several projects, start in 2006

- Fundamental as well as applied research

- Long-term, high-quality sensing in harsh environments

- Better quality data, obtained online

- Measurements that have previously been impossible

- Enabling new science, answering fundamental questions related to decision making, natural hazard early-warning

- More than 35 people, 17 PhD students

NCCR MICS National Competence Center In Research Mobile Information and Communication Systems Bundesamt für Umwelt BAFU Schweizerische Eidgenossenschaft Confédération suisse Confédérazione Svizzera Confederaziun svizra

# Our patient does not fit into a laboratory

# So the laboratory has to go on the mountain

### **Our Field Sites: Precision Scientific Instruments**

### Miniature Low-Power Wireless Sensors

- Static, low-rate sensing (120 sec)

- Simple scalar values: voltages, resistivity, digital sensors

- 4-5 years operation (~150 μA avg. power)

- ~0.1 Mbyte/node/day

- 8+ years experience, ~1'276'035'519 data points

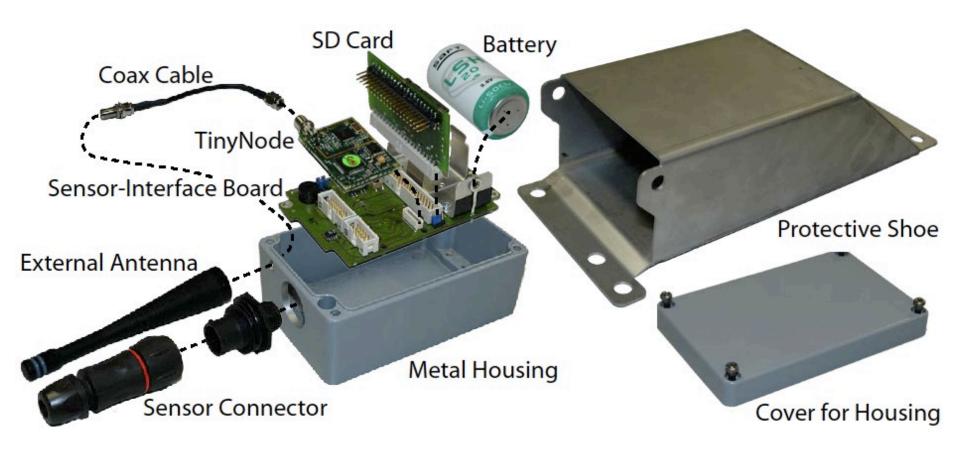

## **Ruggedized for Alpine Extremes**

**E** *H* zürich

[A. Hasler et al: *Wireless Sensor Networks in Permafrost Research - Concept, Requirements, Implementation and Challenges.* Proc. 9th International Conference on Permafrost (NICOP), 2008.]

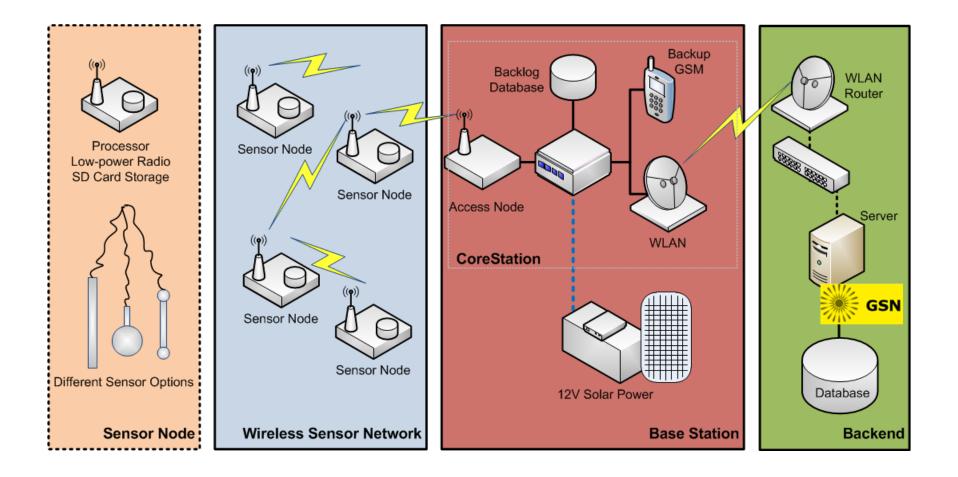

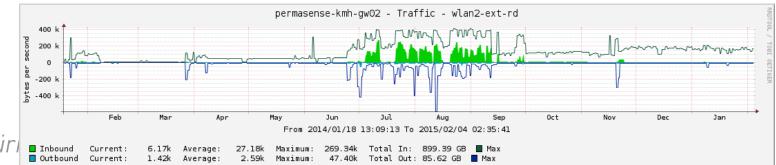

# A base station collects and relays the data to the valley

[B. Buchli, F. Sutton, J. Beutel and L. Thiele: Dynamic Power Management for Long-Term Energy Neutral Operation of Solar Energy Harvesting Systems. Proc. SenSys 2014.

B. Buchli, F. Sutton, J. Beutel and L. Thiele: Towards Enabling Uninterrupted Long-Term Operation of Solar Energy Harvesting Embedded Systems. Proc. EWSN 2014.

M. Keller, J. Beutel and L. Thiele: The Problem Bit. Proc. DCOSS 2013 ★ Best Paper Award ★

B. Buchli, D. Aschwanden and J. Beutel: Battery State-of-Charge Approximation for Energy Harvesting Embedded Systems. Proc. EWSN 2013.

M. Keller, J. Beutel and L. Thiele: How Was Your Journey? Uncovering Routing Dynamics in Deployed Sensor Networks with Multi-hop Network Tomography. Proc. SenSys 2012.]

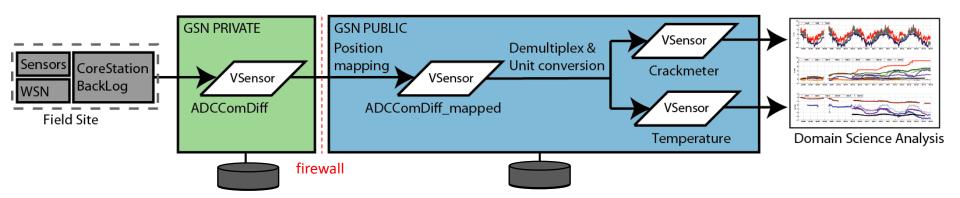

### PermaSense Core System Architecture

**ETH** zürich

[J. Beutel et al: *PermaDAQ: A Scientific Instrument for Precision Sensing and Data Recovery under Extreme Conditions.* Proc. IPSN/SPOTS 2009.]

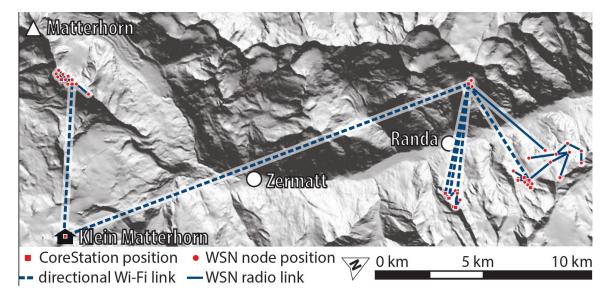

### WLAN Long-haul Communication

- WLAN (802.11a) backbone using directional links

- Leased fiber/DSL from Zermatt Bergbahnen AG to mountaintop

### **Online Data Management & Access**

- Global Sensor Network (GSN)

- Data streaming framework from EPFL (K. Aberer)

- Organized in "virtual sensors", i.e. data types/semantics

- Hierarchies and concatenation of virtual sensors enable on-line processing

- Dual architecture translates data from machine representation to SI values, adds metadata

Data from field site is received by the private GSN server "as is" and **stored** in a primary database.

Data is passed on to a public GSN server where it is **mapped** to metadata (positions, sensor types, calibration) and **converted** to convenient data formats. Data is available for download and analysis using external tools.

# OPPORTUNITIES FOR NETWORKED EMBEDDED SYSTEMS RESEARCH

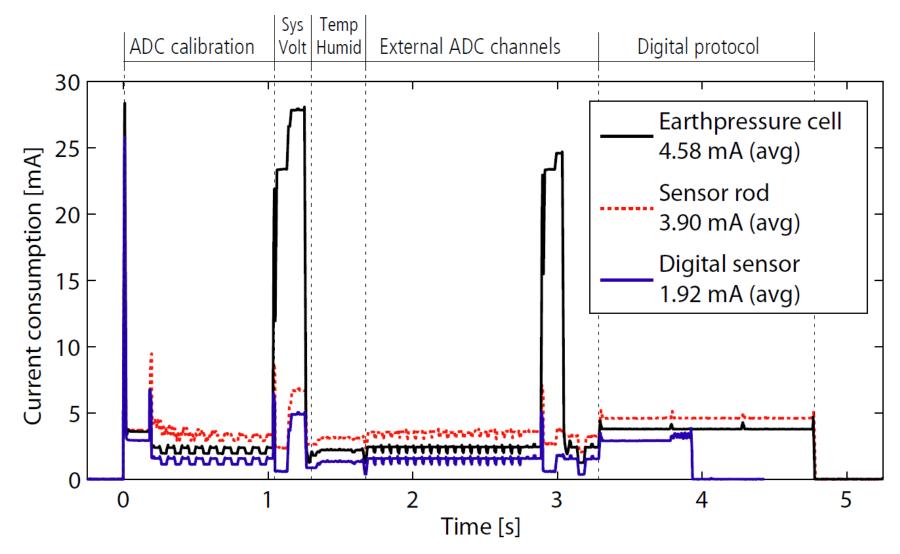

## Sensor Node Hardware

- Shockfish TinyNode184

- MSP430, 16-bit, 8MHz, 8k SRAM, 92k Flash

- LP Radio: SX1211 @ 868 MHz

- Waterproof housing and connectors

- Sensor interface board

- Interfaces, power control

- Temp/humidity monitor

- 1 GB Flash memory

- 3-year life-time

- Single Li-SOCl<sub>2</sub> battery, 13 Ah

- ~300 μA power budget

[J. Beutel et al: *PermaDAQ: A Scientific Instrument for Precision Sensing and Data Recovery under Extreme Conditions.* Proc. IPSN/SPOTS 2009.]

# Ultra Low-Power Data Gathering

- Dozer ultra low-power data gathering system

- Beacon based, 1-hop synchronized TDMA

- Optimized for ultra-low duty cycles

- 0.167% duty-cycle, 0.032mA (@ 30sec beacons)

- Dynamic adaptation

- Back off randomization for diversity

- Jitter adaptation over multiple hops

- Account for long-term loss of connectivity

[Burri, N., von Rickenbach, P., & Wattenhofer, R.: *Dozer: Ultra-Low Power Data Gathering in Sensor Networks.* Proc. IPSN 2007.]

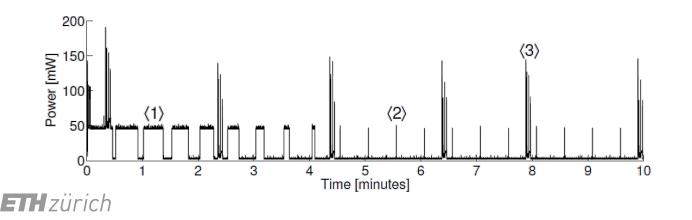

# SIB: Total Power Performance Analysis

| Operating Mode Characterization                                                                                                                                                                               | [mA]         | ]               |                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------|-------------------|

| Sleep                                                                                                                                                                                                         | 0.026        |                 |                   |

| DAQ active <sup><math>a</math></sup>                                                                                                                                                                          | 2.086        |                 |                   |

| Dozer RX idle                                                                                                                                                                                                 | 13.64        |                 |                   |

| Dozer RX                                                                                                                                                                                                      | 14.2         |                 |                   |

| Dozer TX                                                                                                                                                                                                      | 54.6         |                 |                   |

| Measured Average Values                                                                                                                                                                                       | [mA]         | 1/120 sec       |                   |

| DAQ only (2min)                                                                                                                                                                                               | 0.110        |                 | 1/30 sec          |

| Dozer only $(30 \text{sec}/2 \text{min})^b$                                                                                                                                                                   | 0.072        |                 | ,                 |

| $\begin{tabular}{lllllllllllllllllllllllllllllllllll$                                                                                                                                                         | 0.148        |                 |                   |

| <sup>a</sup> Averages power consumption measured over a DAQ routine execution without attached sensor <sup>b</sup> Dozer only includes communication, not including initialization and access to flash memory | -            |                 |                   |

| Sleep                                                                                                                                                                                                         | Functional s | system overhead |                   |

| ;<br>0.034 m/<br>sys                                                                                                                                                                                          | Ż<br>DAQ     | 0.076 mA        | 0.038 mA<br>DOZER |

| 0%                                                                                                                                                                                                            | 20%          | 40% 60%         | 80% 100%          |

|                                                                                                                                                                                                               |              | Ŷ               |                   |

148 uA average power

### Sensors Contribute to Power Consumption

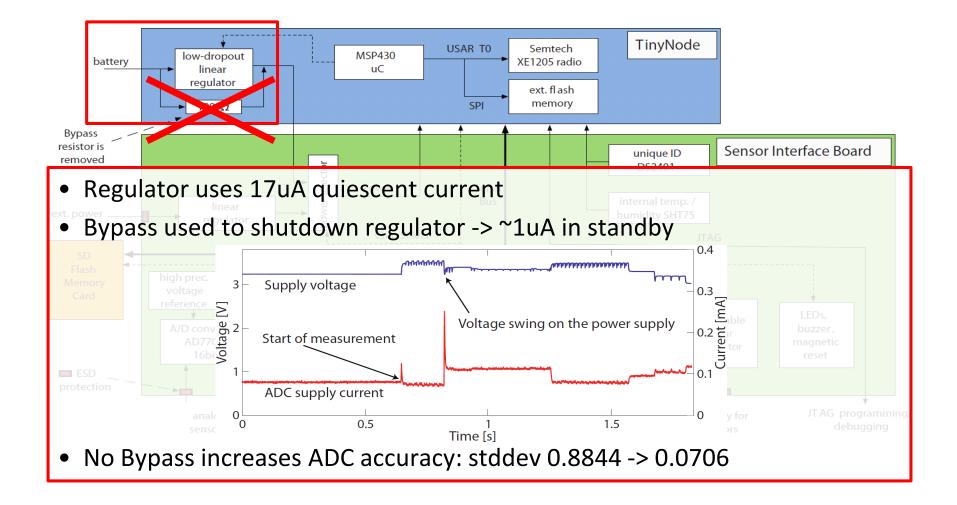

### TinyNode Power Optimization – Squeeze with Implications

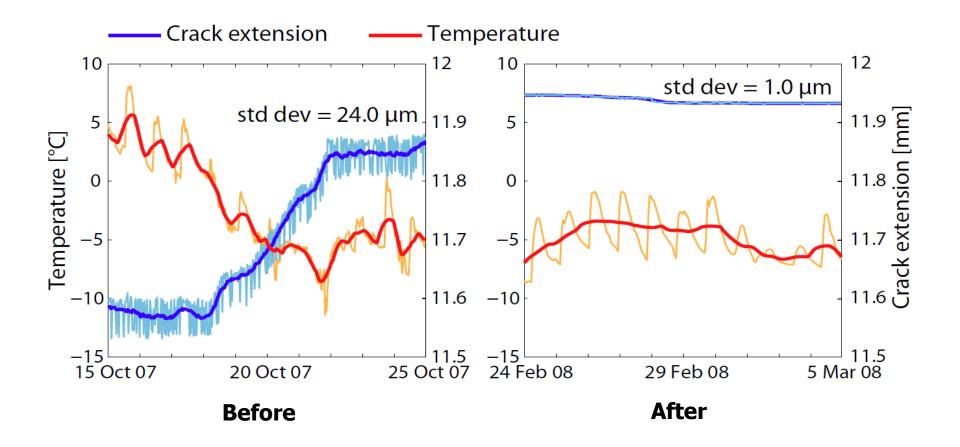

### Power Quality Increases Data Accuracy

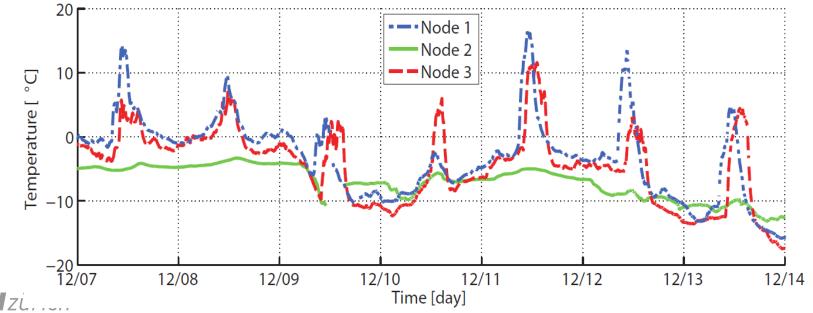

# Challenge: The Physical Environment

- Strong daily variation of temperature

- − −30°C to +40°C

- $\Delta T \leq 20^{\circ}C/hour$

- Impact on

- timing, energy availability, fatigue, SOFTWARE, ...

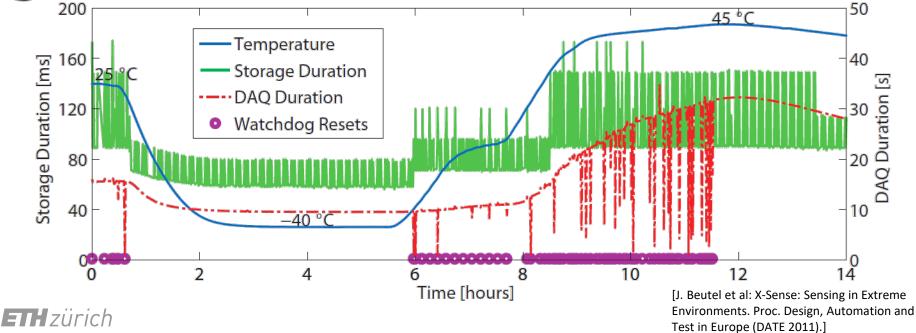

## Impact of Environmental Extremes

- Tighter guard times increase energy efficiency

- Software testing in a climate chamber

- Clock drift compensation yields ± 5ppm

- Validation of correct function

# Global vs. Local Time Sync

- In cases where no network-wide time synchronization is available

- Global time sync not available for network protocol control

- Implications on data usage

- Solution: Elapsed time on arrival

- Sensor nodes measure/accumulate packet sojourn time

- Base station annotates packets with UTC timestamps

- Generation time is calculated as difference  $\tilde{t}_g = t_b \tilde{t}_s$

[M. Keller, J. Beutel and L. Thiele: *Multi-hop network tomography: path reconstruction and per-hop arrival time estimation from partial information.* ACM SIGMETRICS Performance Evaluation Review Volume 40, Issue 1, p. 421-422, 2012.

M. Keller, J. Beutel and L. Thiele: *How Was Your Journey? Uncovering Routing Dynamics in Deployed Sensor Networks with Multi-hop Network Tomography.* Proc. SenSys 2012.]

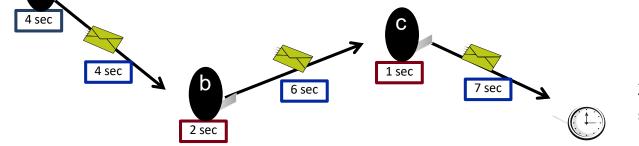

2011/04/14 10:03:31 - 7 sec = 2011/04/14 10:03:24

# Today's Hot Researcher & Paper

- Margaret Martonosi

- Faculty at Princeton

- Computer architecture and mobile computing with a particular focus on power-efficiency.

- Wattch power modeling infrastructure

- IEEE and ACM Fellow

- "For contributions in power-aware computing"

David Brooks, Vivek Tiwari, and Margaret Martonosi (2000). *Wattch: a framework for architectural-level power analysis and optimizations*. 27th Annual International Symposium on Computer Architecture (ISCA '00).: p. 83–94.

# Recap of Today

- Modern embedded hardware (equally for high performance SoCs) offer a great feature set

- Many integrated peripherals/options

- Meticulous attention to power performance in all operating modes

- Software control is increasingly difficult

- Lack of support by design flow/tools

- Overall system complexity

- Profiling methods necessary to assess system level performance

- Detailed figures in documentations work only for each unique case

- Modeling capabilities are limited (we will discuss this in detail)